# **ST7267**

# **USB 2.0 HIGH SPEED MASS STORAGE MICROCONTROLLER**

### PRELIMINARY DATA

- USB 2.0 Interface compliant with Mass Storage Device Class

- Integrated USB 2.0 PHY

- Supports USB High Speed and Full Speed

- 1 control endpoint with two 64-byte buffers

- 1 IN 64-byte bulk / interrupt endpoint

- 1 OUT 64-byte bulk / interrupt endpoint

- 1 IN 512-byte double buffer bulk endpoint

- 1 OUT 512-byte double buffer bulk endpoint

- Suspend and Resume operations

### Mass Storage Controller Interface (MSCI)

- 16-bit RISC Core

- Supports all types of NAND Flash devices

- Reed-Solomon Encoder/Decoder for MLC NAND Flash support: on-the-fly correction (4 bytes of a 512-byte block)

### Memories

- 54K of ROM

- 4 Kbytes of RAM with up to 256 bytes stack

- 2 Kbytes of MSCI CODE RAM

- 5 Kbytes of dual-ported RAM

### Embedded 8-bit ST7 MCU

- Supply Management

- 3.3V operation

- Integrated 3.3V-1.8V voltage regulator

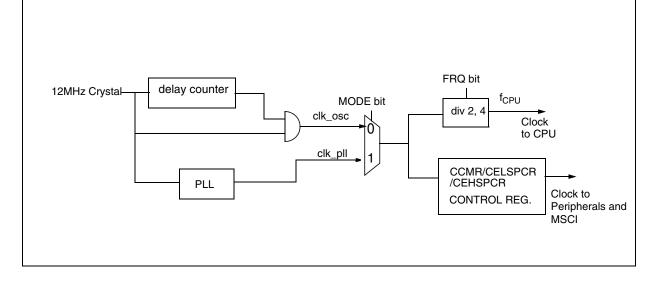

### Clock Management

Integrated PLL for generating core and USB 2.0 clock sources using an external 12 MHz crystal

### Interrupt Management

- 11 Interrupt vectors plus TRAP and RESET

- 40 I/Os interrupt source mapped on 5 vectors

- Nested interrupt management

### I/O Ports

- Up to 40 general purpose I/O port pins

- Two 5V tolerant I/Os

- Communication Interface

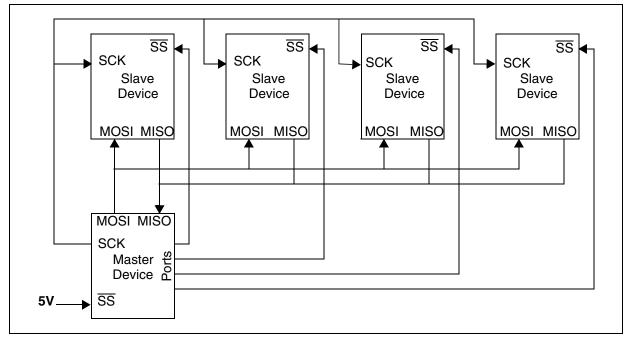

- 1 SPI Synchronous serial interface

- Timers

- Configurable Watchdog for system reliability

- 16-bit timer

- Time Base Unit

- TQFP48 7x7 and TQFP64 10x10 lead-free packages

- Development Support

- Complete reference design including BOM and gerber files

- Supports Windows ME, Windows 2K, Windows XP. Drivers available for Windows

- SE

- Complete application package available to design a USB 2.0 Flash Drive application

| Features                    | ST7267C8                | ST7267R8     |  |  |  |  |  |  |

|-----------------------------|-------------------------|--------------|--|--|--|--|--|--|

| Program memory              | 54K                     |              |  |  |  |  |  |  |

| User RAM (stack) - bytes    | 4K (256                 | 6)           |  |  |  |  |  |  |

| Peripherals                 | WDG, TBU, Time          | r, SPI, MSCI |  |  |  |  |  |  |

| USB interface               | USB 2.                  | 0            |  |  |  |  |  |  |

| # of NAND devices supported | 4                       |              |  |  |  |  |  |  |

| Operating Supply            | 2.7V to 3               | .6V          |  |  |  |  |  |  |

| Operating Temperature       | 0°C to +7               | 0°C to +70°C |  |  |  |  |  |  |

| Packages                    | TQFP48 7x7 TQFP64 10x10 |              |  |  |  |  |  |  |

| 1.1     | RELATED DOCUMENTATION                  | 7  |

|---------|----------------------------------------|----|

| 2 PIN I | DESCRIPTION                            | 9  |

|         | REGISTER & MEMORY MAP                  |    |

| 3.1     | PAGED MEMORY SPACE                     | 17 |

| 3.2     | INTERRUPT AND VECTOR REMAPPING         | 17 |

| 4 ST7   | CENTRAL PROCESSING UNIT                | 23 |

| 4.1     | INTRODUCTION                           | 23 |

| 4.2     | MAIN FEATURES                          | 23 |

| 4.3     | CPU REGISTERS                          | 23 |

| 5 ST7   | POWER SAVING MODES                     | 26 |

| 5.1     | INTRODUCTION                           | 26 |

| 5.2     | WAIT MODE                              | 26 |

| 5.3     | HALT MODE                              | 27 |

|         | 5.3.1 HALT MODE RECOMMENDATIONS        | 27 |

| 6 ST7   | I/O PORTS                              | 29 |

| 6.1     | INTRODUCTION                           | 29 |

| 6.2     | FUNCTIONAL DESCRIPTION                 | 29 |

|         | 6.2.1 Input Modes                      | 29 |

|         | 6.2.2 Output Modes                     |    |

|         | 6.2.3 Alternate Functions              |    |

|         | ST7 I/O PORT IMPLEMENTATION            |    |

|         | UNUSED I/O PINS                        |    |

|         | LOW POWER MODES                        |    |

| 6.6     | INTERRUPTS                             | 32 |

| 6.7     | REGISTER DESCRIPTION                   | 33 |

| 7 ST7   | INTERRUPTS                             | 35 |

| 7.1     | INTRODUCTION                           | 35 |

| 7.2     | MASKING AND PROCESSING FLOW            | 35 |

| 7.3     | INTERRUPTS AND LOW POWER MODES         | 37 |

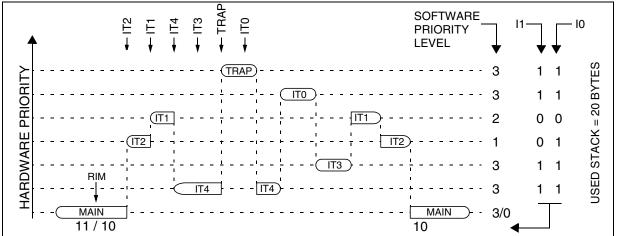

| 7.4     | CONCURRENT & NESTED MANAGEMENT         | 37 |

| 7.5     | INTERRUPT VECTOR TABLE MANAGEMENT      | 39 |

| 7.6     | EXTERNAL INTERRUPTS                    | 40 |

|         | 7.6.1 Software and Hardware Priorities | 40 |

|         | 7.6.2 Enable and Sensitivity Controls  |    |

|         | 7.6.3 Status Flag                      |    |

|         | INTERRUPT REGISTER DESCRIPTION         |    |

|         | CLOCK, RESET AND SUPPLY MANAGEMENT     |    |

|         | CLOCK SYSTEM                           |    |

| 8.2     | CLOCK MANAGEMENT                       | 49 |

|         | 8.2.1 Register Description             |    |

| 8.3     | RESET SEQUENCE MANAGER (RSM)           |    |

|         | 8.3.1 Introduction                     | 52 |

57

\_

|      | 8.3.2          | Asynchronous External RESET pin |    |

|------|----------------|---------------------------------|----|

|      | 8.3.3<br>8.3.4 | Internal Watchdog RESET         |    |

| 84   |                | Y MANAGEMENT                    |    |

|      |                |                                 |    |

|      |                | IP PERIPHERALS                  |    |

|      |                | HDOG TIMER (WDG)                |    |

|      | 10.1.1         | Introduction                    |    |

|      | 10.1.2         |                                 |    |

|      | 10.1.3         | Functional Description          | 56 |

|      |                | Generating a Software reset     |    |

|      |                | Software Watchdog Option        |    |

|      |                | Hardware Watchdog Option        |    |

|      |                | Low Power Modes                 |    |

|      |                |                                 |    |

|      |                | Register Description            |    |

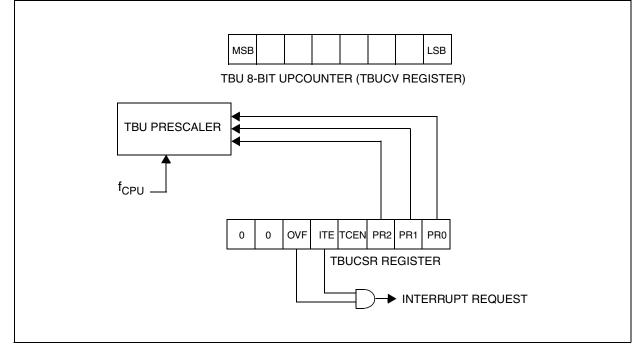

| 10.2 |                | ASE UNIT (TBU)                  |    |

|      | 10.2.1         | Introduction                    | 59 |

|      | 10.2.2         | Main Features                   | 59 |

|      |                | Functional Description          |    |

|      |                | Programming Example             |    |

|      |                | Low Power Modes                 |    |

|      | 10.2.6         | Interrupts                      |    |

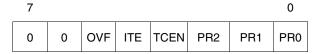

| 10.3 | -              | TIMER                           |    |

|      | 10.3.1         | Introduction                    | 62 |

|      | 10.3.2         | Main Features                   | 62 |

|      |                | Functional Description          |    |

|      |                | Low Power Modes                 |    |

|      |                | Interrupts                      |    |

|      |                | Summary of Timer modes          |    |

| 10.4 |                |                                 |    |

|      |                |                                 |    |

|      |                | Main Features                   |    |

|      | 10.4.3         | General Description             | 81 |

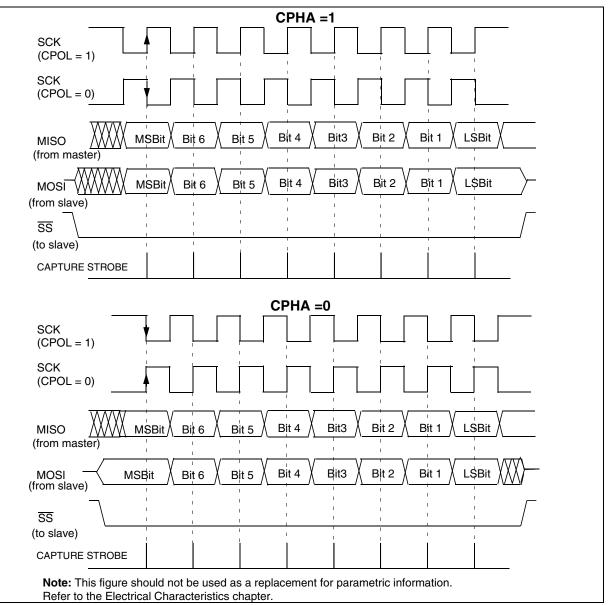

|      |                | Clock Phase and Clock Polarity  |    |

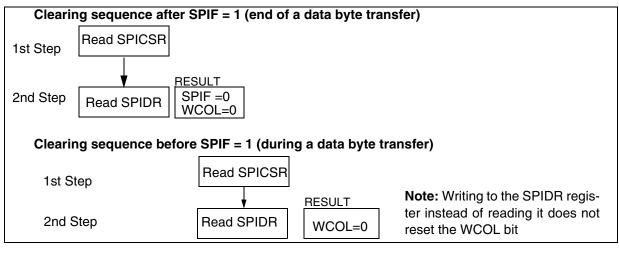

|      |                | Error Flags                     |    |

|      |                | Low Power Modes                 |    |

|      | 10.4.7         |                                 |    |

| 10.5 |                | Register Description            |    |

| 10.0 |                |                                 |    |

|      |                | Main Features                   |    |

|      |                | Functional Description          |    |

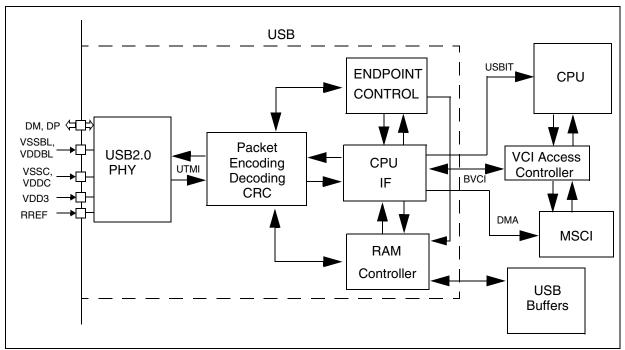

|      |                | USB2.0 PHY                      |    |

|      | 10.5.5         | USB buffers                     | 94 |

| 10.5.6 Register Description                    | . 95 |

|------------------------------------------------|------|

| 10.5.7 Programming consideration               | 104  |

| 10.5.8 USB reset                               | 104  |

| 10.5.9 Suspend /Resume                         | 104  |

| 10.5.10 Endpoint 0 handling                    | 104  |

| 10.5.11 Bulk IN Endpoint                       | 105  |

| 10.5.12 Bulk OUT Endpoint                      |      |

| 10.5.13 Interrupt IN Endpoint                  |      |

| 10.5.14 Interrupt OUT endpoint                 |      |

| 10.5.15 Low Power modes                        |      |

| 10.5.16 Interrupts                             |      |

| 10.5.17 IMPORTANT NOTES                        |      |

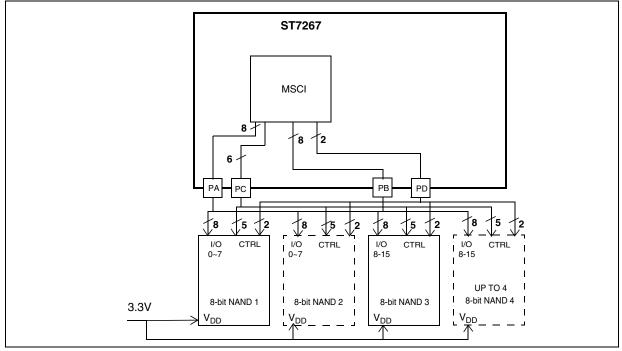

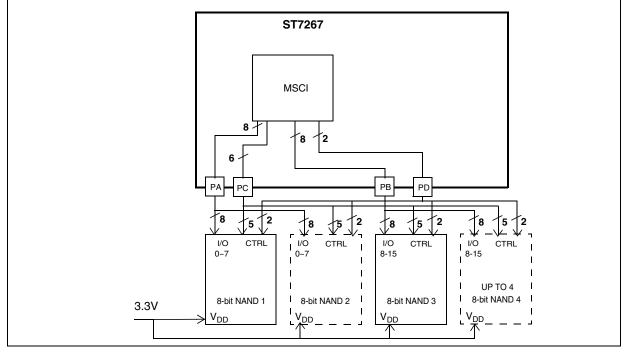

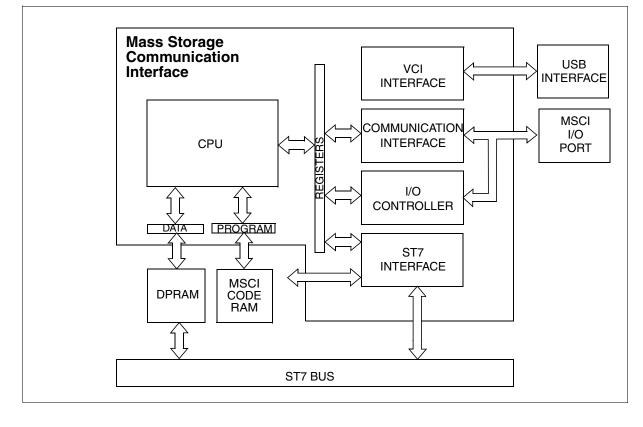

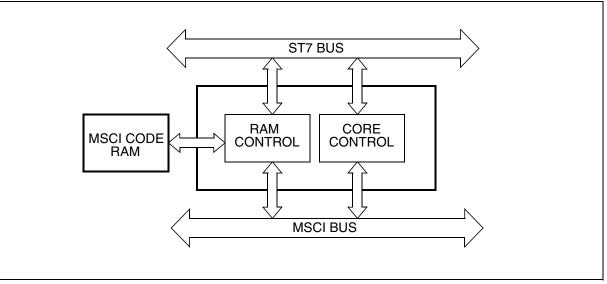

| 11 MASS STORAGE COMMUNICATION INTERFACE (MSCI) |      |

| 11.1 INTRODUCTION                              |      |

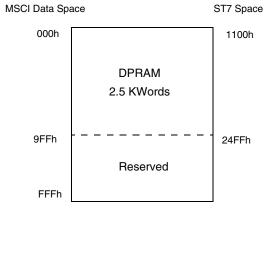

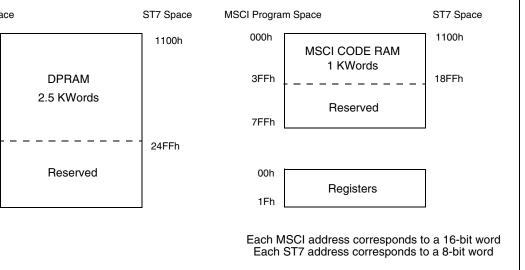

| 12 MSCI REGISTER & MEMORY MAP                  | 111  |

| 13 MSCI CENTRAL PROCESSING UNIT                | 113  |

| 13.1 INTRODUCTION                              | 113  |

| 13.2 MAIN FEATURES                             | 113  |

| 13.3 CPU REGISTERS                             |      |

|                                                |      |

| 14 MSCI ST7 INTERFACE                          |      |

| 14.1 INTRODUCTION                              |      |

| 14.2 FUNCTIONAL DESCRIPTION                    |      |

| 14.2.1 ST7 Control of the MSCI                 |      |

| 14.2.2 Interrupt generation from MSCI to ST7   |      |

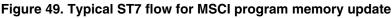

| 14.2.3 Program RAM upload                      |      |

| 14.2.4 ST7 Write Access to MSCI Code RAM       |      |

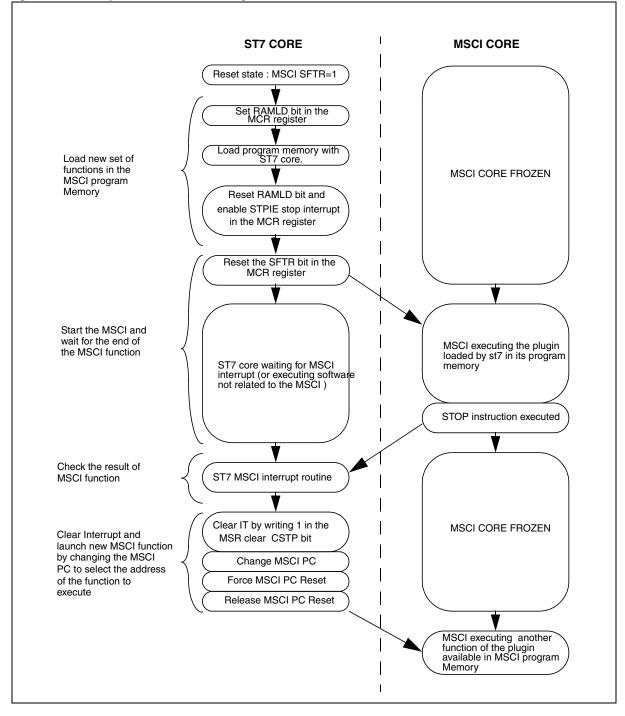

| 14.2.5 Example Control Flow                    |      |

| 14.2.6 ST7 Register Description                |      |

| 14.2.7 Low Power modes                         |      |

| 14.2.8 Interrupts                              |      |

| 15 MSCI I/O CONTROLLER                         |      |

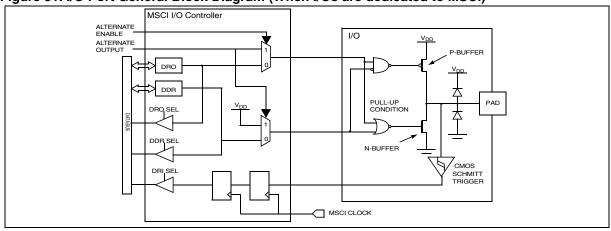

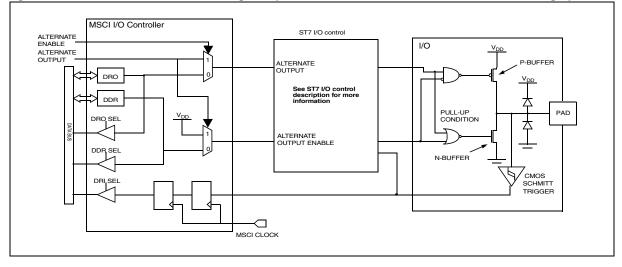

| 15.1 INTRODUCTION                              | 123  |

| 15.2 FUNCTIONAL DESCRIPTION                    | 123  |

| 15.2.1 Input mode                              | 123  |

| 15.2.2 Output mode                             | 123  |

| 15.2.3 Alternate functions                     |      |

| 15.3 I/O SHARING BETWEEN ST7 AND MSCI          | 124  |

| 15.3.1 Register Description                    | 125  |

| 16 MSCI VCI INTERFACE                          |      |

| 16.1 INTRODUCTION                              | 126  |

| 16.2 MAIN FEATURES                             |      |

| 16.3 FUNCTIONAL DESCRIPTION                    |      |

|                                                |      |

| 16.4 ERROR MANAGEMENT                          |      |

| 16.4.1 MSCI VCI Interface Registers            |      |

| 16.4.2 MSCI VCI Interface software example     |      |

| 16.5 USB REGISTER ADDRESSING                   | 134  |

57

\_

| 17 | MSCI PARALLEL INTERFACE                                 | 139 |

|----|---------------------------------------------------------|-----|

|    | 17.1 INTRODUCTION                                       | 139 |

|    | 17.2 FUNCTIONAL DESCRIPTION                             | 139 |

|    | 17.2.1 FIFO management                                  | 140 |

|    | 17.3 CONFIGURING THE CONTROL LINES                      | 142 |

|    | 17.3.1 Control Signal Enable bits                       |     |

|    | 17.3.2 Control Signal Parameters                        |     |

|    | 17.4 MSCI PARALLEL INTERFACE CONFIGURATION EXAMPLES     |     |

|    | 17.4.1 Examples for output mode                         |     |

|    | 17.4.2 Examples for input mode                          |     |

|    | 17.5.1 Double buffer underflow in output mode           |     |

|    | 17.5.2 Double buffer overflow in input mode             |     |

|    | 17.6 ECC GENERATOR                                      |     |

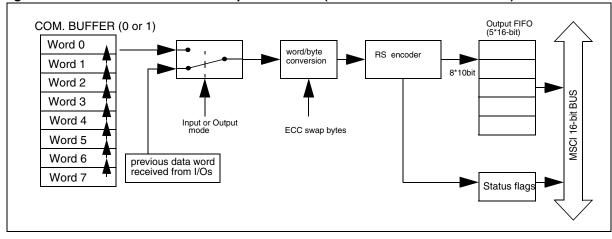

|    | 17.7 REED SOLOMON ENCODER                               | 149 |

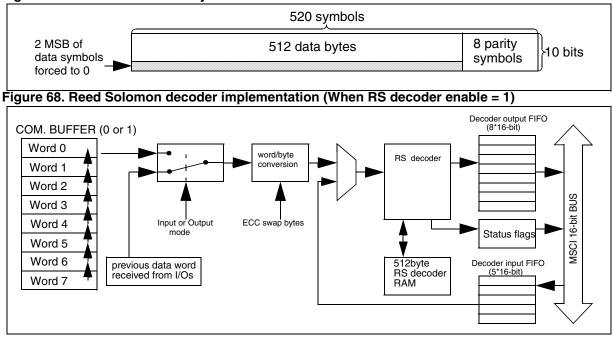

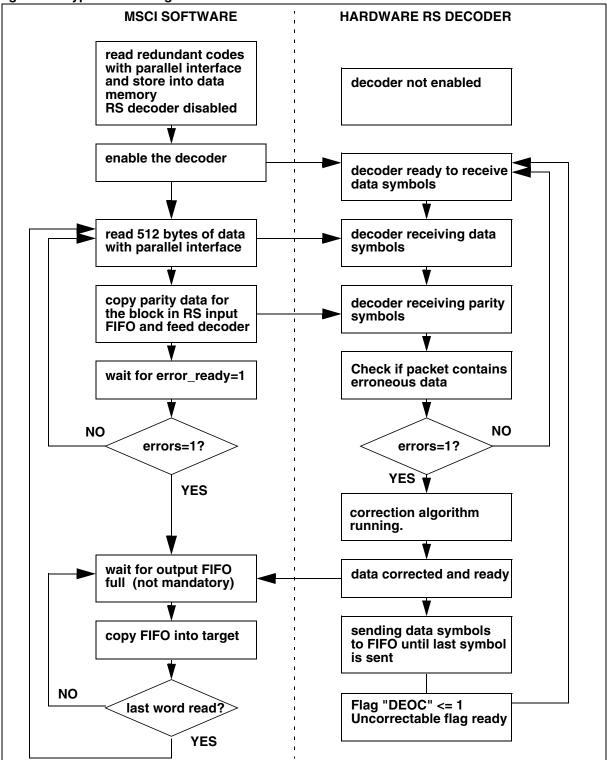

|    | 17.8 REED SOLOMON DECODER                               | 150 |

|    | 17.9 MSCI SOFTWARE EXAMPLES                             | 152 |

|    | 17.9.1 Loop for data send                               | 152 |

|    | 17.9.2 Loop for data read                               | 153 |

|    | 17.10REGISTER DESCRIPTION                               |     |

| 18 | ELECTRICAL CHARACTERISTICS                              |     |

|    | 18.1 PARAMETER CONDITIONS                               |     |

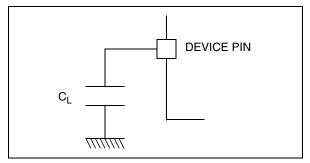

|    | 18.1.1 Minimum and Maximum values                       |     |

|    | 18.1.2 Typical values                                   |     |

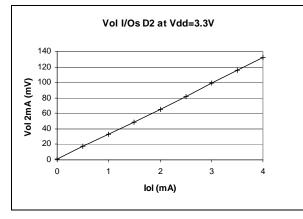

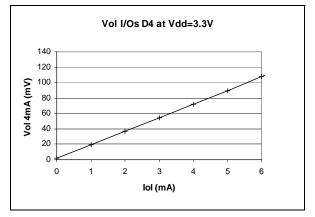

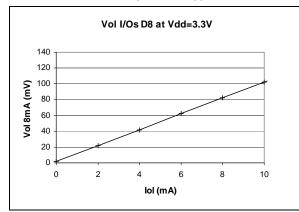

|    | 18.1.3 Typical curves                                   |     |

|    | 18.1.5 Pin input voltage                                |     |

|    | 18.2 ABSOLUTE MAXIMUM RATINGS                           |     |

|    | 18.2.1 Voltage Characteristics                          | 162 |

|    | 18.2.2 Current Characteristics                          | 162 |

|    | 18.2.3 Thermal Characteristics                          |     |

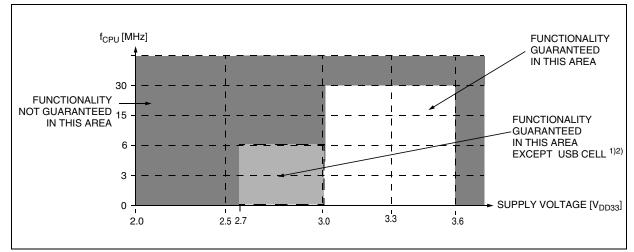

|    | 18.3 OPERATING CONDITIONS                               |     |

|    | 18.3.1 General Operating Conditions                     |     |

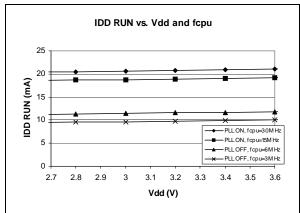

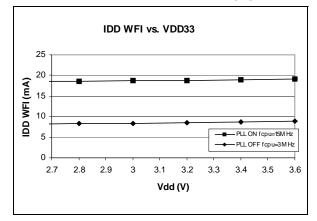

|    | 18.4 SUPPLY CURRENT CHARACTERISTICS                     |     |

|    | 18.4.1 RUN and WAIT Modes                               |     |

|    | 18.4.3 Supply and Clock Managers                        |     |

|    | 18.5 CLOCK AND TIMING CHARACTERISTICS                   |     |

|    | 18.5.1 General Timings                                  | 165 |

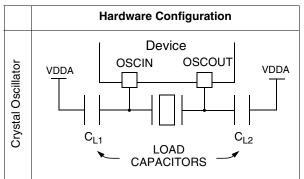

|    | 18.5.2 Crystal Oscillator                               |     |

|    | 18.6 MEMORY CHARACTERISTICS                             | 166 |

|    | 18.6.1 RAM and Hardware Registers                       |     |

|    | 18.7 EMC CHARACTERISTICS                                |     |

|    | 18.7.1 Functional EMS (Electro Magnetic Susceptibility) |     |

|    | 18.7.2 Electro Magnetic Interference (EMI)              | 167 |

| 18.7.3 Absolute Maximum Ratings (Electrical Sensitivity)     |     |

|--------------------------------------------------------------|-----|

| 18.8.1 General Characteristics                               |     |

| 18.8.2 Output Driving Current                                |     |

| 18.9.1 Asynchronous RESET Pin                                |     |

|                                                              |     |

| 18.10.1 Watchdog Timer                                       |     |

| 18.10.3 16-Bit Timer                                         |     |

| 18.110THER COMMUNICATION INTERFACE CHARACTERISTICS           | 175 |

| 18.11.1 MSCI Parallel Interface                              |     |

| 18.11.2 USB (Universal Bus Interface)                        |     |

| 18.11.3 SPI - Serial Peripheral Interface                    |     |

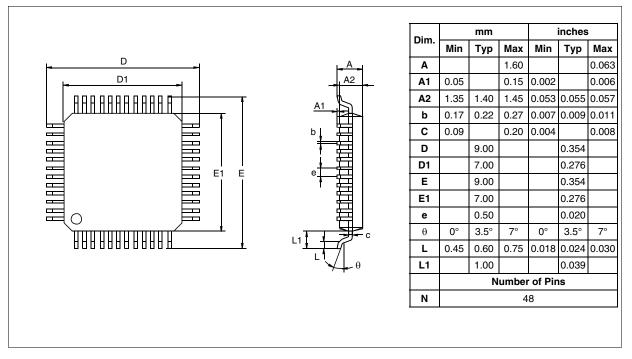

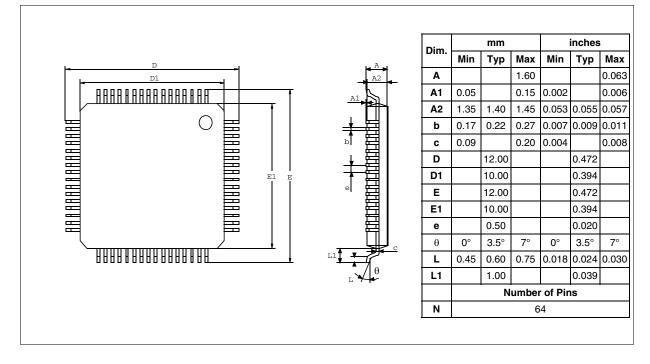

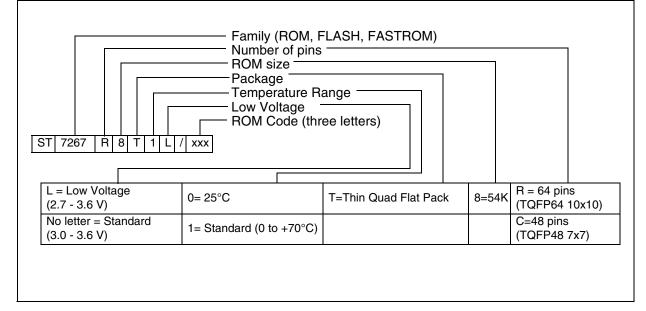

| 19.1 PACKAGE MECHANICAL DATA                                 |     |

| 19.2 THERMAL CHARACTERISTICS                                 |     |

| 20 DEVICE CONFIGURATION AND ORDERING INFORMATION             |     |

| 20.1 OPTION BYTE                                             |     |

| 21 DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE | 183 |

| 22 REVISION HISTORY                                          | 185 |

|                                                              |     |

# **1 INTRODUCTION**

5/

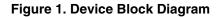

The ST7267 is a USB 2.0 highspeed Mass Storage microcontroller. The USB 2.0 highspeed interface including PHY and function supports USB 2.0 Mass Storage Device Class.

The Mass Storage Controller Interface (MSCI) features a 16-bit RISC ALU core combined with the Reed-Solomon Encoder/Decoder on-the-fly correction on 512 data byte blocks provides a flexible, high transfer rate solution for interfacing all types of NAND Flash memory devices.

The internal 60 MHz PLL driven by the 12 MHz oscillator is used to generate the 480 MHz frequency for the USB 2.0 PHY.

The ST7 CPU runs the application program from the internal ROM and RAM. USB data and patch code are stored in internal RAM. The I/O ports provide functions for EEPROM connection, LEDs and write protect switch control.

The internal 3.3V to 1.8V voltage regulator provides the 1.8V supply voltage to the digital part of the circuit.

### **1.1 RELATED DOCUMENTATION**

For details on the programming model of the ST7 CPU and the MSCI, please refer to the following manuals:

- Mass Storage Controller Interface MSCI 16-bit Core Programming Manual

- ST7 Programming Manual

# INTRODUCTION (Cont'd)

Δ7/

# **2 PIN DESCRIPTION**

<u>(۲</u>/

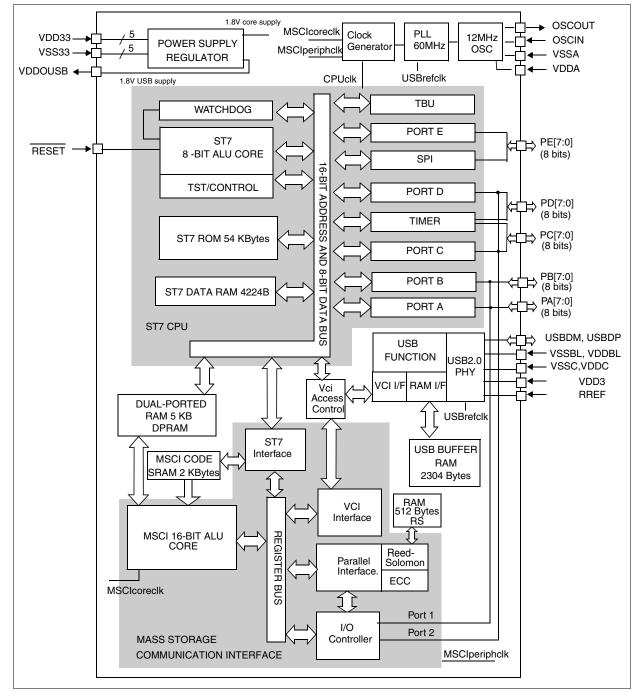

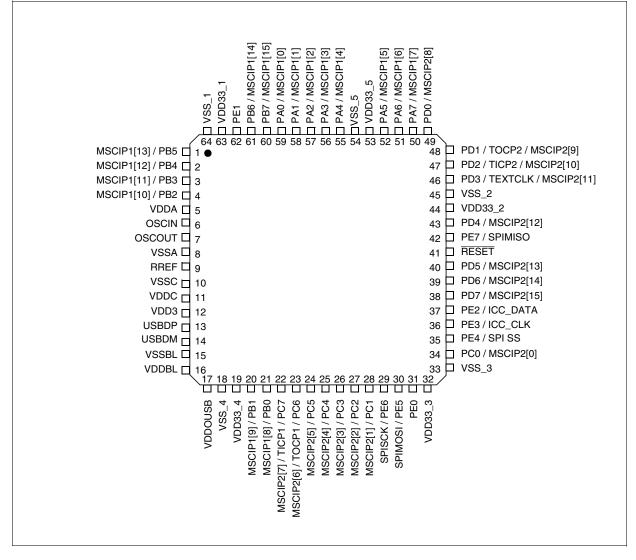

### Figure 2. 48-Pin TQFP Package Pinout

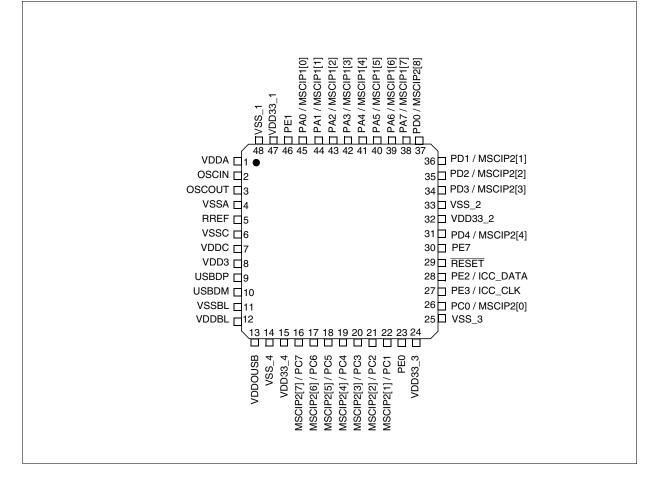

### Figure 3. 64-Pin TQFP Package Pinout

45/

### Legend / Abbreviations for tables 2 thru 6:

| Туре:             | I = input, O = output, S = supply                       |

|-------------------|---------------------------------------------------------|

| Input level:      | A = Dedicated analog input                              |

| In/Output level:r | $C_{T} = CMOS \ 0.3V_{DD}/0.7V_{DD}$ with input trigger |

|                   | T <sub>T</sub> = TTL 0.8V / 2V with Schmitt trigger     |

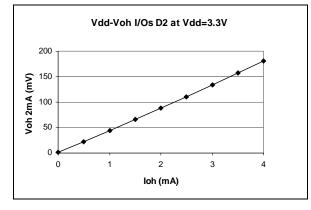

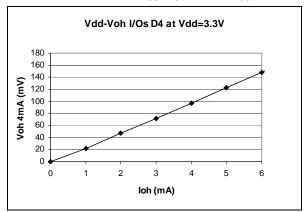

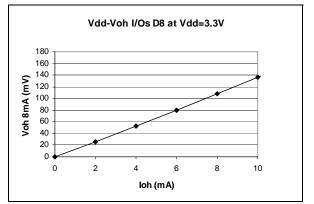

| Output level:     | D8 = 8mA drive                                          |

|                   | D4 = 4mA drive                                          |

|                   | D2 = 2mA drive                                          |

|                   |                                                         |

Port and control configuration:

- Input:float = floating, wpu = weak pull-up, wpd = weak pull-down, int = interrupt

- Output: OD = pseudo open drain, PP = push-pull

### Table 1. Power Supply

| Ρ      | in       |         |      |                                                 |  |  |  |  |

|--------|----------|---------|------|-------------------------------------------------|--|--|--|--|

| TQFP48 | Pin Name |         | Type | Description                                     |  |  |  |  |

| 48     | 64       | VSS_1   | S    | Ground                                          |  |  |  |  |

| 47     | 63       | VDD33_1 | S    | I/Os and Regulator supply voltage               |  |  |  |  |

| 33     | 45       | VSS_2   | S    | Ground                                          |  |  |  |  |

| 32     | 44       | VDD33_2 | S    | I/Os and Regulator supply voltage               |  |  |  |  |

| 25     | 33       | VSS_3   | S    | Ground                                          |  |  |  |  |

| 24     | 32       | VDD33_3 | S    | I/Os and Regulator supply voltage               |  |  |  |  |

| 14     | 18       | VSS_4   | S    | Ground                                          |  |  |  |  |

| 15     | 19       | VDD33_4 | S    | I/Os and Regulator supply voltage               |  |  |  |  |

|        | 54       | VSS_5   | S    | Ground                                          |  |  |  |  |

|        | 53       | VDD33_5 | S    | I/Os supply voltage                             |  |  |  |  |

| 13     | 17       | VDDOUSB | S    | USB PHY, OSC and PLL power supply output (1.8V) |  |  |  |  |

### Table 2. Control & System

47/

| Ρ      | in          |          |      | ~    |                                     |  |  |  |  |

|--------|-------------|----------|------|------|-------------------------------------|--|--|--|--|

| TQFP48 | TQFP64      | Pin Name | Type | Powe | Description                         |  |  |  |  |

| 29     | 29 41 RESET |          |      | 3.3  | Reset input with filter and pull-up |  |  |  |  |

# Table 3. USB 2.0 Interface

| Ρ      | in     |          |      |                                                                                |  |  |  |  |  |  |

|--------|--------|----------|------|--------------------------------------------------------------------------------|--|--|--|--|--|--|

| TQFP48 | TQFP64 | Pin Name | Type | Description                                                                    |  |  |  |  |  |  |

| 12     | 16     | VDDBL    | S    | Supply voltage for buffers and deserialisation ffs (1.8V)                      |  |  |  |  |  |  |

| 11     | 15     | VSSBL    | S    | Ground for buffers and deserialisation ffs (1.8V)                              |  |  |  |  |  |  |

| 10     | 14     | USBDM    | I/O  | USB DATA -                                                                     |  |  |  |  |  |  |

| 9      | 13     | USBDP    | I/O  | USB DATA +                                                                     |  |  |  |  |  |  |

| 8      | 12     | VDD3     | S    | Supply voltage for the FS compliance (3.3V)                                    |  |  |  |  |  |  |

| 7      | 11     | VDDC     | S    | Supply voltage for DLL & xor tree (1.8V)                                       |  |  |  |  |  |  |

| 6      | 10     | VSSC     | S    | Ground for DLL & xor tree (1.8V)                                               |  |  |  |  |  |  |

| 5      | 9      | RREF     | A    | Ref. resistor for integrated impedances process adapt (11.5kohms 1% Pull Down) |  |  |  |  |  |  |

# Table 4. USB 2.0 and core Clock System

| Ρ      | in     |            |   |                                     |  |  |  |  |

|--------|--------|------------|---|-------------------------------------|--|--|--|--|

| TQFP48 | TFQP64 | Pin Name S |   | Description                         |  |  |  |  |

| 4      | 8      | VSSA       | S | Ground for osc & PLL (1.8V)         |  |  |  |  |

| 3      | 7      | OSCOUT     | 0 | 12MHz oscillator output             |  |  |  |  |

| 2      | 6      | OSCIN      | I | 12MHz oscillator input              |  |  |  |  |

| 1      | 5      | VDDA       | S | Supply voltage for osc & PLL (1.8V) |  |  |  |  |

57

# Table 5. General Purpose I/O Ports / Mass Storage I/Os

| Pin    |        |                    |      |             |                |         |       | Int  | Le   | vel | (   | Conf               | igur         | atior      | ı | Main | Alternate f | unation |

|--------|--------|--------------------|------|-------------|----------------|---------|-------|------|------|-----|-----|--------------------|--------------|------------|---|------|-------------|---------|

| P48    | P64    | Pin Name           | Type | 5V tolerant | rt             | uts     | l     | Inpu | t    | Out | put | function<br>(after | Alternate i  | unction    |   |      |             |         |

| TQFP48 | TQFP64 |                    |      | 5V t        | Input          | Outputs | float | ndw  | int  | OD  | ЪР  | reset)             | ALT1         | ALT2       |   |      |             |         |

| 45     | 59     | PA0                | I/O  |             | $T_{T}$        | D4      | Х     | Х    |      | Х   | Х   | Port A0            |              | MSCIP1[0]  |   |      |             |         |

| 44     | 58     | PA1                | I/O  |             | $T_T$          | D4      | Х     | Х    |      | Х   | Х   | Port A1            |              | MSCIP1[1]  |   |      |             |         |

| 43     | 57     | PA2                | I/O  |             | Τ <sub>T</sub> | D4      | Х     | Х    |      | Х   | Х   | Port A2            |              | MSCIP1[2]  |   |      |             |         |

| 42     | 56     | PA3                | I/O  |             | $T_{T}$        | D4      | Х     | Х    | ei0  | Х   | Х   | Port A3            |              | MSCIP1[3]  |   |      |             |         |

| 41     | 55     | PA4                | I/O  |             | Τ <sub>T</sub> | D4      | Х     | Х    | eiu  | Х   | Х   | Port A4            |              | MSCIP1[4]  |   |      |             |         |

| 40     | 52     | PA5                | I/O  |             | Τ <sub>Τ</sub> | D4      | Х     | Х    |      | Х   | Х   | Port A5            |              | MSCIP1[5]  |   |      |             |         |

| 39     | 51     | PA6                | I/O  |             | $T_{T}$        | D4      | Х     | Х    |      | Х   | Х   | Port A6            |              | MSCIP1[6]  |   |      |             |         |

| 38     | 50     | PA7                | I/O  |             | Τ <sub>T</sub> | D4      | Х     | Х    |      | Х   | Х   | Port A7            |              | MSCIP1[7]  |   |      |             |         |

|        | 21     | PB0 <sup>(2)</sup> | I/O  |             | Τ <sub>T</sub> | D4      | Х     | Х    |      | Х   | Х   | Port B0            |              | MSCIP1[8]  |   |      |             |         |

|        | 20     | PB1 <sup>(2)</sup> | I/O  |             | Τ <sub>Τ</sub> | D4      | Х     | Х    |      | Х   | Х   | Port B1            |              | MSCIP1[9]  |   |      |             |         |

|        | 4      | PB2 <sup>(2)</sup> | I/O  |             | Τ <sub>Τ</sub> | D4      | Х     | Х    |      | Х   | Х   | Port B2            |              | MSCIP1[10] |   |      |             |         |

|        | 3      | PB3 <sup>(2)</sup> | I/O  |             | $T_{T}$        | D4      | Х     | Х    | - 14 | Х   | Х   | Port B3            |              | MSCIP1[11] |   |      |             |         |

|        | 2      | PB4 <sup>(2)</sup> | I/O  |             | $T_{T}$        | D4      | Х     | Х    | ei1  | Х   | Х   | Port B4            |              | MSCIP1[12] |   |      |             |         |

|        | 1      | PB5 <sup>(2)</sup> | I/O  |             | $T_{T}$        | D4      | Х     | Х    |      | Х   | Х   | Port B5            |              | MSCIP1[13] |   |      |             |         |

|        | 61     | PB6 <sup>(2)</sup> | I/O  |             | $T_{T}$        | D4      | Х     | Х    |      | Х   | Х   | Port B6            |              | MSCIP1[14] |   |      |             |         |

|        | 60     | PB7 <sup>(2)</sup> | I/O  |             | Τ <sub>Τ</sub> | D4      | Х     | Х    |      | Х   | Х   | Port B7            |              | MSCIP1[15] |   |      |             |         |

| 26     | 34     | PC0                | I/O  |             | $T_{T}$        | D8      | Х     | Х    |      | Х   | Х   | Port C0            |              | MSCIP2[0]  |   |      |             |         |

| 22     | 28     | PC1                | I/O  |             | $T_{T}$        | D8      | Х     | Х    |      | Х   | Х   | Port C1            |              | MSCIP2[1]  |   |      |             |         |

| 21     | 27     | PC2                | I/O  |             | Τ <sub>Τ</sub> | D8      | Х     | Х    |      | Х   | Х   | Port C2            |              | MSCIP2[2]  |   |      |             |         |

| 20     | 26     | PC3                | I/O  |             | $T_{T}$        | D8      | Х     | Х    | -:0  | Х   | Х   | Port C3            |              | MSCIP2[3]  |   |      |             |         |

| 19     | 25     | PC4                | I/O  |             | $T_{T}$        | D4      | Х     | Х    | ei2  | Х   | Х   | Port C4            |              | MSCIP2[4]  |   |      |             |         |

| 18     | 24     | PC5                | I/O  |             | $T_{T}$        | D4      | Х     | Х    |      | Х   | Х   | Port C5            |              | MSCIP2[5]  |   |      |             |         |

| 17     | 23     | PC6                | I/O  |             | Τ <sub>Τ</sub> | D4      | Х     | Х    |      | Х   | Х   | Port C6            | Timer OCP1   | MSCIP2[6]  |   |      |             |         |

| 16     | 22     | PC7                | I/O  |             | $T_{T}$        | D4      | Х     | Х    |      | Х   | Х   | Port C7            | Timer ICP1   | MSCIP2[7]  |   |      |             |         |

| 37     | 49     | PD0                | I/O  |             | Τ <sub>Τ</sub> | D2      | Х     | Х    |      | Х   | Х   | Port D0            |              | MSCIP2[8]  |   |      |             |         |

| 36     | 48     | PD1                | I/O  |             | Τ <sub>Τ</sub> | D2      | Х     | Х    |      | Х   | Х   | Port D1            | Timer OCP2   | MSCIP2[9]  |   |      |             |         |

| 35     | 47     | PD2                | I/O  |             | $T_{T}$        | D2      | Х     | Х    |      | Х   | Х   | Port D2            | Timer ICP2   | MSCIP2[10] |   |      |             |         |

| 34     | 46     | PD3                | I/O  |             | Τ <sub>Τ</sub> | D2      | Х     | Х    | a:0  | Х   | Х   | Port D3            | Timer EXTCLK | MSCIP2[11] |   |      |             |         |

| 31     | 43     | PD4                | I/O  |             | Τ <sub>Τ</sub> | D2      | Х     | Х    | ei3  | Х   | Х   | Port D4            |              | MSCIP2[12] |   |      |             |         |

|        | 40     | PD5 <sup>(2)</sup> | I/O  |             | Τ <sub>Τ</sub> | D2      | Х     | Х    | 1    | Х   | Х   | Port D5            |              | MSCIP2[13] |   |      |             |         |

|        | 39     | PD6 <sup>(2)</sup> | I/O  |             | $T_{T}$        | D2      | Х     | Х    | 1    | Х   | Х   | Port D6            |              | MSCIP2[14] |   |      |             |         |

|        | 38     | PD7 <sup>(2)</sup> | I/O  |             | $T_T$          | D2      | Х     | Х    | 1    | Х   | Х   | Port D7            |              | MSCIP2[15] |   |      |             |         |

| Pi     | in   | Level Configuration Main |      | Main     | Altornato f          | unction |   |     |                        |    |                    |         |          |      |

|--------|------|--------------------------|------|----------|----------------------|---------|---|-----|------------------------|----|--------------------|---------|----------|------|

| P48    | P64  | Pin Name                 | Type | tolerant | olera<br>ut ti Input |         | t | Out | Output function (after |    | Alternate function |         |          |      |

| TQFP48 | TQFI |                          |      | 5V t     | Input                | Outputs |   | ndm | int                    | OD | ΡР                 | reset)  | ALT1     | ALT2 |

| 23     | 31   | PE0                      | I/O  |          | Τ <sub>Τ</sub>       | D8      | Х | Х   |                        | Х  | Х                  | Port E0 |          |      |

| 46     | 62   | PE1                      | I/O  |          | Τ <sub>Τ</sub>       | D8      | Х | Х   |                        | Х  | Х                  | Port E1 |          |      |

| 28     | 37   | PE2                      | I/O  |          | $T_T$                | D8      | Х | Х   |                        | Х  | Х                  | Port E2 | ICC_DATA |      |

| 27     | 36   | PE3 <sup>(1)</sup>       | I/O  |          | $T_T$                | D8      | Х | Х   | ei4                    | Х  | Х                  | Port E3 | ICC_CLK  |      |

|        | 35   | PE4 <sup>(2)</sup>       | I/O  |          | $T_T$                | D2      | Х | Х   | 614                    | Х  | Х                  | Port E4 | SPI SS   |      |

|        | 30   | PE5 <sup>(2)</sup>       | I/O  |          | $T_T$                | D2      | Х | Х   |                        | Х  | Х                  | Port E5 | SPI MOSI |      |

|        | 29   | PE6 <sup>(2)</sup>       | I/O  | Х        | Τ <sub>Τ</sub>       | D2      | Х | Х   |                        | Х  | Х                  | Port E6 | SPI SCK  |      |

| 30     | 42   | PE7                      | I/O  | Х        | $T_T$                | D2      | Х | Х   |                        | Х  | Х                  | Port E7 | SPI MISO |      |

### Notes:

**1. Caution**: during normal operation this pin must be pulled-up, internally or externally. This is to avoid entering ICC mode unexpectedly during a reset. In the application, even if the pin is configured as output, any reset will put it back in pull-up

2. Ports unavailable in the 48-pin packages (PB7:0, PD7:5, PE6:4) are forced to input mode with internal pull-up activated to avoid possible floating I/O consumption.

# Table 6. NAND Interface Pin Assignment for different applications

| NAND 16-bit parallel ac-<br>cess through 4 CEs <sup>(1)</sup> | IO[0-7] | IO[8-15] | ALE | CLE | WE  | RE  | CE1 | CE2                | CE3                | CE4                | RnB | WP  |

|---------------------------------------------------------------|---------|----------|-----|-----|-----|-----|-----|--------------------|--------------------|--------------------|-----|-----|

| ST7267 pins                                                   | PA0-7   | PB0-7    | PC0 | PC1 | PC2 | PC3 | PC4 | PC5 <sup>(2)</sup> | PC6 <sup>(2)</sup> | PC7 <sup>(2)</sup> | PD0 | PD1 |

### Notes:

**\$7**

1. when 8-bit NANDs are connected, the TQFP48 package can be used

2. if only one NAND is used, these I/Os are free for other applications

### Table 7. NAND Interface Pin Assignment (2 or 4 8-bit NANDs)

| NAND Pin   | I/O0-7 | ALE | CLE | WE  | RE  | CE1 | I/O8-15 | CE2                | RnB | WP  |

|------------|--------|-----|-----|-----|-----|-----|---------|--------------------|-----|-----|

| ST7267 pin | PA0-7  | PC0 | PC1 | PC2 | PC3 | PC4 | PB0-7   | PC5 <sup>(1)</sup> | PD0 | PD1 |

### Note:

1. When two NANDs have to be handled, this I/O is free for other functions. Pins from different chips should be tied together (i.e. CLE1 with CLE2...).

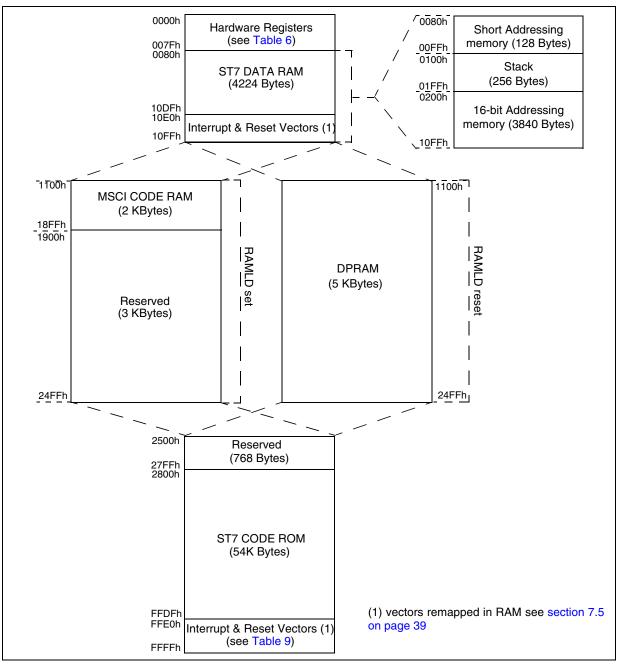

# **3 ST7 REGISTER & MEMORY MAP**

As shown in Figure 6, the ST7 core is capable of addressing 64K bytes of memories and I/O registers.

The available memory locations consist of:

- 80 bytes of register locations

- 4 Kbytes of ST7 DATA RAM (including up to 256 bytes for the stack from 0100h to 01FFh).

- 54 Kbytes of ST7 CODE ROM program memory

- The highest address bytes contain the user reset and interrupt vectors in ROM which are remapped in ST7 DATA RAM.

Two memory spaces are addressable by both the ST7 and the MSCI

- 2 Kbytes of MSCI CODE RAM

- 5 Kbytes of dual-ported RAM

### **3.1 PAGED MEMORY SPACE**

57

The MSCI CODE RAM and the DPRAM are mapped in the same address range on the ST7 bus (1100h to 24FFh).

During initialisation, the MSCI program code has to be loaded in the MSCI CODE RAM by the ST7

To do this, set the RAMLD bit in the MSCI Control Register (MCR). This can only be done while the MSCI is reset state. Refer to section 14.2.3 on page 116 for details.

When the MSCI code is loaded, clear the RAMLD bit to disable any further access to MSCI CODE RAM from the ST7 bus.

For a description of the MSCI Register and Memory Map, refer to section 12 on page 111.

### **3.2 INTERRUPT AND VECTOR REMAPPING**

For flexibility, the interrupt and reset vectors can be mapped in RAM. See section 7.5 on page 39.

**IMPORTANT**: Memory locations noted "Reserved" must never be accessed. Accessing a reserved area generates a hardware reset of the device.

### Figure 6. ST7 Memory Map

| Table 8. | Hardware | Register | Memory | / Мар |

|----------|----------|----------|--------|-------|

|----------|----------|----------|--------|-------|

57

| @     | Block   | Register Label | Register name                               | Reset<br>Status    | Remarks |

|-------|---------|----------------|---------------------------------------------|--------------------|---------|

| 0000h |         | PWRR           | PoWeR management Register                   | 20h                | r/w     |

| 0001h |         | FADDR          | Function ADDress Register                   | 00h                | r/w     |

| 0002h |         |                | Not used. Always return 00h                 |                    |         |

| 0003h |         | ITINR          | Interrupt EP0 and IN EP Register            | 00h                | r       |

| 0004h |         |                | Not used. Always return 00h                 |                    |         |

| 0005h |         | ITOUTR         | Interrupt OUT EP Register                   | 00h                | r       |

| 0006h |         |                | Not used. Always return 00h                 |                    |         |

| 0007h |         | ITINER         | Interrupt IN Enable Register                | 07h                | r/w     |

| 0008h |         |                | Not used. Always return 00h                 |                    |         |

| 0009h |         | ITOUTER        | Interrupt OUT Enable Register               | 06h                | r/w     |

| 000Ah |         | ITUSBER        | Interrupt USB Enable Register               | 06h                | r/w     |

| 000Bh |         | ITUSBR         | Interrupt USB Register                      | 00h                | r       |

| 000Ch | USBHS   | FRNBRM         | FRame NumBer Register (MSB)                 | 00h                | r       |

| 000Dh | 03003   | FRNBRL         | FRame NumBer Register (LSB)                 | 00h                | r       |

| 000Eh |         | TSTMODE        | TeST MODEs                                  | 00h                | r/w     |

| 000Fh |         | INDEXR         | INDEX Register                              | 00h                | r/w     |

| 0010h |         | INMAXPRM       | IN EP n Max Pkt size Register (MSB)         | 00h                | r/w     |

| 0011h |         | INMAXPRL       | IN EP n Max Pkt size Register (LSB)         | 00h                | r/w     |

| 0012h |         | INCSRM         | IN EP n Control Status Register (MSB)       | 00h                | r/w     |

| 0013h |         | INCSRL         | Control Status Reg for EP0 or IN EP n (LSB) | 00h                | r/w     |

| 0014h |         | OUTMAXPRM      | OUT EP n Max Pkt size Register (MSB)        | 00h                | r/w     |

| 0015h |         | OUTMAXPRL      | OUT EP n Max Pkt size Register (LSB)        | 00h                | r/w     |

| 0016h |         | OUTCSRM        | OUT EP n Control Status Register (MSB)      | 00h                | r/w     |

| 0017h |         | OUTCSRL        | OUT EP n Control Status Register (LSB)      | 00h                | r/w     |

| 0018h |         | OUTCNTRM       | OUT EP n Count Register (MSB)               | 00h                | r       |

| 0019h |         | OUTCNTRL       | OUT EP n Count Register (LSB)               | 00h                | r       |

| 001Ah |         |                |                                             |                    |         |

| to    |         |                | Reserved (6 Bytes)                          |                    |         |

| 001Fh |         |                |                                             |                    |         |

| 0020h |         |                |                                             |                    |         |

| 0021h |         | EP0DR          | Endpoint 0 Data Register                    | xxh                | r/w     |

| 0022h |         |                |                                             |                    |         |

| 0023h | USBHS   | EP1DR          | Endpoint 1 Data Register                    | xxh                | r/w     |

| 0024h |         |                |                                             |                    |         |

| 0025h |         | EP2DR          | Endpoint 2 Data Register                    | xxh                | r/w     |

| 0026h |         | PADR           | Port A Data Register                        | 00h <sup>(1)</sup> | r/w     |

| 0027h |         | PADDR          | Port A Data Direction Register              | 00h                | r/w     |

| 0028h | ST7 I/O | PAOR           | Port A Option Register                      | 00h                | r/w     |

| 0029h | Ports   | PBDR           | Port B Data Register                        | 00h <sup>(1)</sup> | r/w     |

| 002Ah |         | PBDDR          | Port B Data Direction Register              | 00h                | r/w     |

| 002Bh |         | PBOR           | Port B Option Register                      | 00h                | r/w     |

| @     | Block   | Register Label | Register name                             | Reset<br>Status    | Remarks |

|-------|---------|----------------|-------------------------------------------|--------------------|---------|

| 002Ch |         | PCDR           | Port C Data Register                      | 00h <sup>(1)</sup> | r/w     |

| 002Dh |         | PCDDR          | Port C Data Direction Register            | 00h                | r/w     |

| 002Eh |         | PCOR           | Port C Option Register                    | 00h                | r/w     |

| 002Fh |         | PDDR           | Port D Data Register                      | 00h <sup>(1)</sup> | r/w     |

| 0030h | ST7 I/O | PDDDR          | Port D Data Direction Register            | 00h                | r/w     |

| 0031h | Ports   | PDOR           | Port D Option Register                    | 00h                | r/w     |

| 0032h |         | PEDR           | Port E Data Register                      | 00h <sup>(1)</sup> | r/w     |

| 0033h |         | PEDDR          | Port E Data Direction Register            | 00h                | r/w     |

| 0034h |         | PEOR           | Port E Option Register                    | 00h                | r/w     |

| 0035h |         | WDGCR          | Watchdog Control Register                 | 7Fh                | r/w     |

| 0036h | WDG     |                |                                           |                    |         |

| 0037h |         | ISPR0          | Interrupt Software Priority Register 0    | FFh                | r/w     |

| 0038h |         | ISPR1          | Interrupt Software Priority Register 1    | FFh                | r/w     |

| 0039h |         | ISPR2          | Interrupt Software Priority Register 2    | FFh                | r/w     |

| 003Ah |         | ISPR3          | Interrupt Software Priority Register 3    | FFh                | r/w     |

| 003Bh |         | EICR0          | External Interrupt Control Register 0     | 00h                | r/w     |

| 003Ch |         | EICR1          | External Interrupt Control Register 1     | 00h                | r/w     |

| 003Dh |         | PAEIENR        | Port A External Interrupt Enable register | 00h                | r/w     |

| 003Eh | ITO     | PBEIENR        | Port B External Interrupt Enable register | 00h                | r/w     |

| 003Fh | ITC     | PCEIENR        | Port C External Interrupt Enable register | 00h                | r/w     |

| 0040h |         | PDEIENR        | Port D External Interrupt Enable register | 00h                | r/w     |

| 0041h |         | PEEIENR        | Port E External Interrupt Enable register | 00h                | r/w     |

| 0042h |         | PAEISR         | Port A External Interrupt Status Register | 00h                | r/w     |

| 0043h |         | PBEISR         | Port B External Interrupt Status Register | 00h                | r/w     |

| 0044h |         | PCEISR         | Port C External Interrupt Status Register | 00h                | r/w     |

| 0045h |         | PDEISR         | Port D External Interrupt Status Register | 00h                | r/w     |

| 0046h |         | PEEISR         | Port E External Interrupt Status Register | 00h                | r/w     |

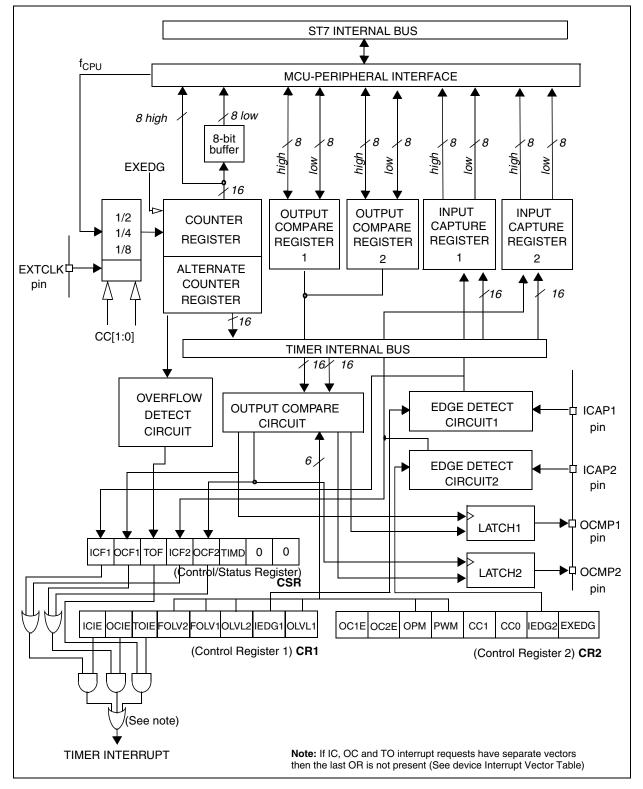

| 0047h |         | TCR2           | Timer Control Register 2                  | 00h                | r/w     |

| 0048h |         | TCR1           | Timer Control Register 1                  | 00h                | r/w     |

| 0049h |         | TCSR           | Timer Control/Status Register             | xxh                | r       |

| 004Ah |         | TIC1HR         | Timer Input Capture 1 High Register       | xxh                | r       |

| 004Bh |         | TIC1LR         | Timer Input Capture 1 Low Register        | xxh                | r       |

| 004Ch |         | TOC1HR         | Timer Output Compare 1 High Register      | 80h                | r/w     |

| 004Dh |         | TOC1LR         | Timer Output Compare 1 Low Register       | 00h                | r/w     |

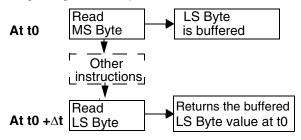

| 004Eh | TIMER   | TCHR           | Timer Counter High Register               | FFh                | r       |

| 004Fh |         | TCLR           | Timer Counter Low Register                | FCh                | r       |

| 0050h |         | TACHR          | Timer Alternate Counter High Register     | FFh                | r       |

| 0051h |         | TACLR          | Timer Alternate Counter Low Register      | FCh                | r       |

| 0052h |         | TIC2HR         | Timer Input Capture 2 High Register       | xxh                | r       |

| 0053h |         | TIC2LR         | Timer Input Capture 2 Low Register        | xxh                | r       |

| 0054h |         | TOC2HR         | Timer Output Compare 2 High Register      | 80h                | r/w     |

| 0055h |         | TOC2LR         | Timer Output Compare 2 Low Register       | 00h                | r/w     |

| 0056h | MISC    | MISCR1         | Miscellaneous Register 1                  | 00h                | r/w     |

57

| @     | Block              | Register Label | Register name                               | Reset<br>Status | Remarks |  |  |

|-------|--------------------|----------------|---------------------------------------------|-----------------|---------|--|--|

| 0057h |                    |                | Reserved (1 Byte)                           |                 |         |  |  |

| 0058h | тры                | TBUCVR         | TBU Counter Value Register                  | 00h             | r/w     |  |  |

| 0059h | TBU                | TBUCSR         | TBU Control/Status Register                 | 00h             | r/w     |  |  |

| 005Ah |                    |                | Reserved (1 Byte)                           |                 | I       |  |  |

| 005Bh |                    | CCMR           |                                             | 00h             | r/w     |  |  |

| 005Ch |                    | CELSPCR        | CKGEN Control Mode Register                 | 00h             | r/w     |  |  |

| 005Dh | CKGEN              | CEHSPCR        | CKGEN Enable of Low Speed Periph. CLK Reg.  | 00h             | r/w     |  |  |

| 005Eh |                    |                | CKGEN Enable of High Speed Periph. CLK Reg. |                 |         |  |  |

| 005Fh | 500                | EOSSR          | End Of Suspend Status Register              | 00h             | r/w     |  |  |

| 0060h | EOS                | EOSCR          | End Of Suspend Control Register             | 00h             | r/w     |  |  |

| 0061h |                    | SPIDR          | SPI Data I/O register                       | xxh             | r/w     |  |  |

| 0062h | SPI                | SPICR          | SPI Control Register                        | 0xh             | r/w     |  |  |

| 0063h |                    | SPICSR         | SPI Control/Status Register                 | 00h             | r       |  |  |

| 0064h |                    |                |                                             |                 |         |  |  |

| to    | Reserved (5 Bytes) |                |                                             |                 |         |  |  |

| 0068h |                    |                |                                             |                 |         |  |  |

| 0069h |                    | MCR            | MSCI Control Register                       | 01h             | r/w     |  |  |

| 006Ah |                    | MSR            | MSCI Status Register                        | 00h             | r/w     |  |  |

| 006Bh |                    | MPCM           | MSCI PC register (MSB)                      | 00h             | r/w     |  |  |

| 006Ch | MSCI               | MPCL           | MSCI PC register (LSB)                      | 00h             | r/w     |  |  |

| 006Dh |                    | MCRCH          | MSCI CRC (MSB)                              | 00h             | r       |  |  |

| 006Eh |                    | MCRCL          | 00h                                         | r               |         |  |  |

| 006Fh |                    |                |                                             |                 |         |  |  |

| 0070h |                    |                |                                             |                 |         |  |  |

| to    |                    |                | Reserved (4 Bytes)                          |                 |         |  |  |

| 0073h |                    |                |                                             |                 |         |  |  |

| 0074h |                    | DMCR           | Debug Module Control Register               | 00h             | r/w     |  |  |

| 0075h |                    | DMCSR          | Debug Module Control / Status Register      | 10h             | r/w     |  |  |

| 0076h |                    | DMBK1M         | Debug Module BreaKpoint 1 register (MSB)    | FFh             | r/w     |  |  |

| 0077h |                    | DMBK1L         | Debug Module BreaKpoint 1 register (LSB)    | FFh             | r/w     |  |  |

| 0078h | DM <sup>(2)</sup>  | DMBK2M         | Debug Module BreaKpoint 2 register (MSB)    | FFh             | r/w     |  |  |

| 0079h |                    | DMBK2L         | Debug Module BreaKpoint 2 register (LSB)    | FFh             | r/w     |  |  |

| 007Ah |                    | DMCR2          | Debug Module Control Register 2             | 00h             | r/w     |  |  |

| 007Bh |                    | DMCSR2         | Debug Module Control / Status Register 2    | 00h             | r       |  |  |

| 007Ch |                    | DMENFCT        | Debug Module Enable Function register       | FFh             | r/w     |  |  |

# **Legend**: x=undefined, r/w=read/write **Notes**:

1. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

2. For a description of the registers of the Debug Module used for In-Circuit Debugging, see ICC reference manual.

# Table 9. Interrupt Mapping

| N° | Source<br>Block | Description                  | Register<br>Label | Priority<br>Order | Exit<br>from<br>HALT | Address<br>Vector |

|----|-----------------|------------------------------|-------------------|-------------------|----------------------|-------------------|

|    | RESET           | Reset vector                 |                   |                   | yes                  | FFFEh-FFFFh       |

|    | TRAP            | Software Interrupt vector    | N/A Highest       |                   | no                   | FFFCh-FFFDh       |

| 0  |                 | NMI Interrupt                |                   | Priority          |                      | FFFAh-FFFBh       |

| 1  | USB             | USB Interrupt                | see Note 1        |                   | no                   | FFF8h-FFF9h       |

| 2  | EOS             | USB End of Suspend Interrupt |                   | T I               | yes                  | FFF6h-FFF7h       |

| 3  | MSCI            | MSCI interrupt               | MSCI              | T I               | no                   | FFF4h-FFF5h       |

| 4  | El0             | External Interrupt Port A    | N/A               | Ī                 | yes                  | FFF2h-FFF3h       |

| 5  | El1             | External Interrupt Port B    | N/A               | T I               | yes                  | FFF0h-FFF1h       |

| 6  | El2             | External Interrupt Port C    | N/A               | T I               | yes                  | FFEEh-FFEFh       |

| 7  | El3             | External Interrupt Port D    | N/A               | T I               | yes                  | FFECh-FFEDh       |

| 8  | El4             | External Interrupt Port E    | N/A               | ↓                 | yes                  | FFEAh-FFEBh       |

| 9  | SPI             | SPI interrupt                | SPICSR            | Lowest            | yes                  | FFE8h-FFE9h       |

| 10 | TIMER           | Timer interrupt              | T1SR              | Priority          | no                   | FFE6h-FFE7h       |

| 11 | TBU             | TimeBase Unit                | TBUCSR            |                   | no                   | FFE4h-FFE5h       |

Note 1: please see USB chapter

# **4 ST7 CENTRAL PROCESSING UNIT**

# **4.1 INTRODUCTION**

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

### **4.2 MAIN FEATURES**

- Enable executing 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes (with indirect addressing mode)

- Two 8-bit index registers

- 16-bit stack pointer

- Low power HALT and WAIT modes

- Priority maskable hardware interrupts

- Non-maskable software/hardware interrupts

### **4.3 CPU REGISTERS**

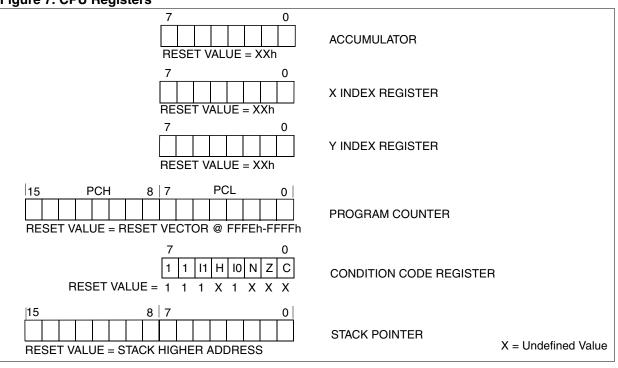

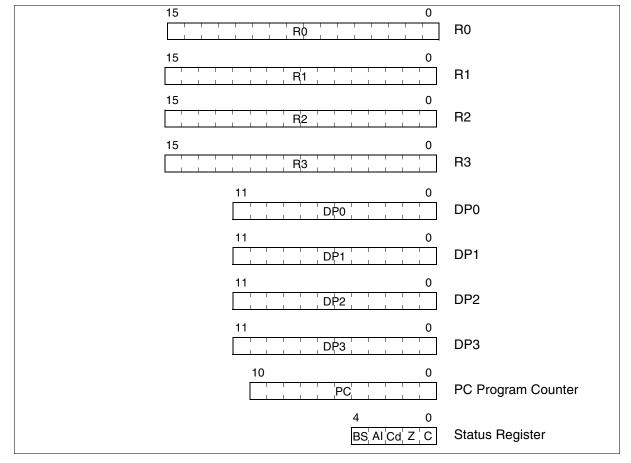

The 6 CPU registers shown in Figure 7 are not present in the memory mapping and are accessed by specific instructions.

### Figure 7. CPU Registers

5/

### Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

### Index Registers (X and Y)

These 8-bit registers are used to create effective addresses or as temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures.

### **Program Counter (PC)**

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

# CENTRAL PROCESSING UNIT (Cont'd) Condition Code Register (CC)

Read/Write

Reset Value: 111x1xxx

| 7 |   |    |   |    |   |   | 0 |

|---|---|----|---|----|---|---|---|

| 1 | 1 | 11 | Н | 10 | Ν | Z | С |

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

### **Arithmetic Management Bits**

### Bit 4 = **H** Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

### Bit 2 = N Negative.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It's a copy of the result  $7^{th}$  bit.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative

(i.e. the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

### Bit 1 = **Z** Zero.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

0: The result of the last operation is different from zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

### Bit 0 = C Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

### **Interrupt Management Bits**

### Bit 5,3 = 11, 10 Interrupt

The combination of the I1 and I0 bits gives the current interrupt software priority.

| Interrupt Software Priority   | 11 | 10 |

|-------------------------------|----|----|

| Level 0 (main)                | 1  | 0  |

| Level 1                       | 0  | 1  |

| Level 2                       | 0  | 0  |

| Level 3 (= interrupt disable) | 1  | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (IxSPR). They can be also set/ cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See the interrupt management chapter for more details.

# CENTRAL PROCESSING UNIT (Cont'd) STACK POINTER (SP)

Read/Write

5/

Reset Value: 01FFh

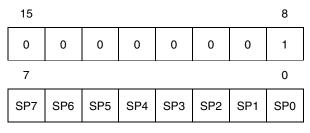

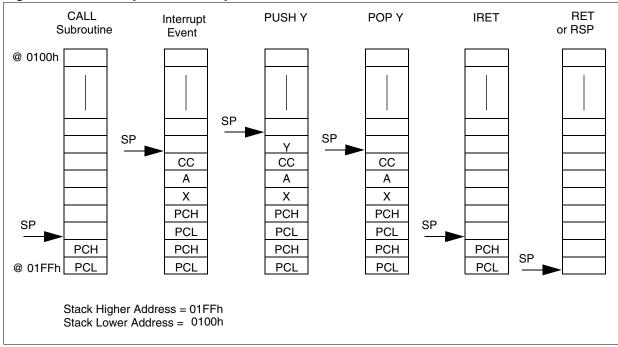

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 8).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following a CPU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP6 to SP0 bits are set) which is the stack higher address.

### Figure 8. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 8.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

# **5 ST7 POWER SAVING MODES**

### **5.1 INTRODUCTION**

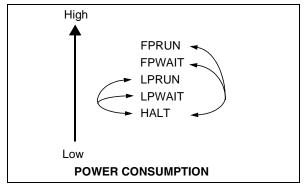

To give a large measure of flexibility to the application in terms of power consumption, three main power saving modes are implemented in the Device (see Figure 9):

- Low Power Mode (PLL OFF)

- Wait

- Halt

After a RESET low power mode is selected by default. This mode drives the Device (CPU and embedded peripherals except USB) by means of a master clock which is based on the main oscillator frequency.

From this low power mode, different modes may be selected using specific CPU instruction.

**Important note:** Moreover, if the USB cell is not used, the UPO bit of the EOSCR register must be set to avoid any USB2 PHY consumption.

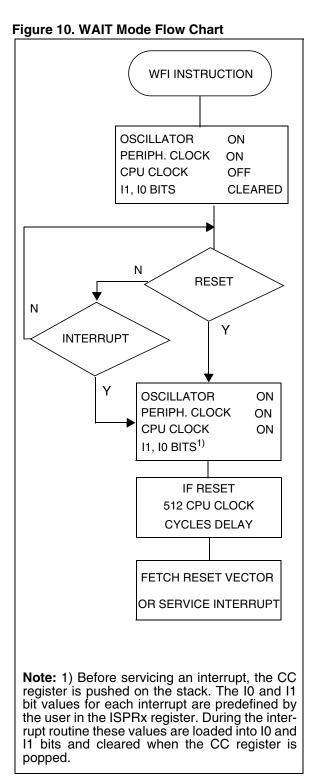

### 5.2 WAIT MODE

WAIT mode places the Device in a low power consumption mode by stopping the CPU.

This power saving mode is selected by executing the "WFI" CPU instruction.

All peripherals remain active. During WAIT mode, the I bits in the CC register are forced to 0, enabling all interrupts. All other registers and memory remain unchanged. The Device remains in WAIT mode until an interrupt or reset occurs. If the event is an interrupt, the program counter immediately branches to the starting address of the interrupt or reset service routine. If the wake up event is a reset, before fetching the reset vector, there is a 512 CPU clock cycle delay to allow for stabilization. Refer to Figure 10.

### ST7 POWER SAVING MODES (Cont'd)

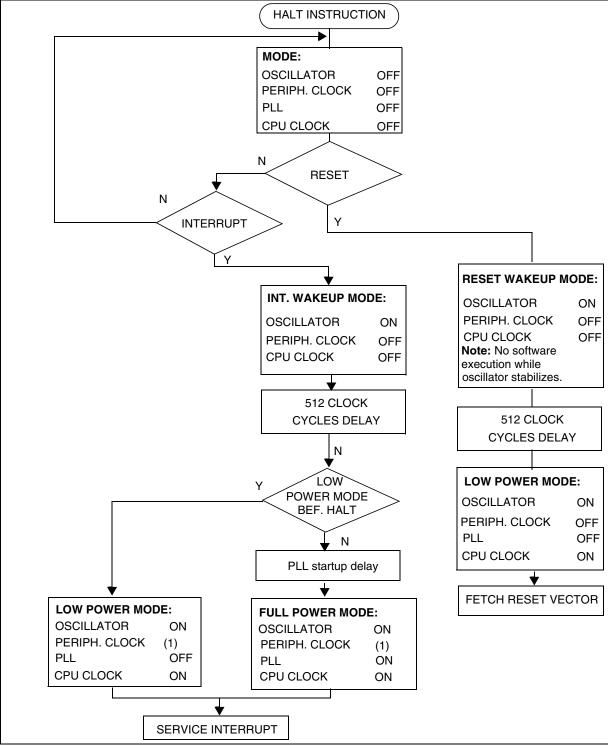

### 5.3 HALT MODE

HALT mode is the lowest power consumption mode. HALT mode is entered by executing the HALT instruction. The internal oscillator is stopped, causing all internal processing to be stopped, including the operation of the on-chip peripherals.

To further decrease the consumption (especially for the Suspend mode):

- The internal regulator must be put in powerdown mode by setting the REG\_OFF bit of the CCMR register.

- The active slew rate compensation cell of the IOs must be stopped by setting the CPO bit of the EOSCR register.

Entering HALT mode clears the I bits in the CC register, enabling interrupts. If an interrupt is pending, the Device wakes up immediately. Not all interrupts will wake up the Device from HALT, only those listed in the Interrupt Mapping Table in the Interrupt section allow wake-up.

Specific interrupts such as an external interrupt or an USB end of suspend interrupt (as described in Table 16) or a reset wakes up the Device from HALT mode.

- If a reset is the wake-up event, the main oscillator is immediately turned on and a 512 CPU cycle delay is used to stabilize the oscillator. After the start up delay the device starts in Low power mode and the CPU resumes operation by fetching the reset vector.

- If an interrupt is the wake-up event, the main oscillator is immediately turned on and a 512 CPU cycle delay is used to stabilize the oscillator. After the start up delay, if the device was in low

5/

power mode before entering in halt mode the device starts in low power mode and the CPU resumes operation. But if the device was in full power mode before entering in halt, the operation are resumed only after the PLL lock

Refer to Figure 11 for more details.

### 5.3.1 HALT MODE RECOMMENDATIONS

- Make sure that an external event is available or that the USB end of suspend interrupt is enabled to wake up the Device from Halt mode.

- When using an external interrupt to wake up the Device, reinitialize the corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT instruction. The main reason for this is that the I/O may be wrongly configured due to external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the level sensitiveness of each external interrupt as a precautionary measure.

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the I bits in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering other peripheral interrupt routines after executing the external interrupt routine corresponding to the wake-up event (reset or external interrupt).

# ST7 POWER SAVING MODES (Cont'd)

### Figure 11. HALT Mode Flow Chart

<sup>1)</sup> periph. clock status is the one before the halt according to CER register.

# 6 ST7 I/O PORTS

### **6.1 INTRODUCTION**

The I/O ports allow data transfer. An I/O port can contain up to 8 pins. Each pin can be programmed independently either as a digital input or digital output. In addition, specific pins may have several other functions. These functions can include external interrupt, alternate signal input/output for onchip peripherals or analog input.

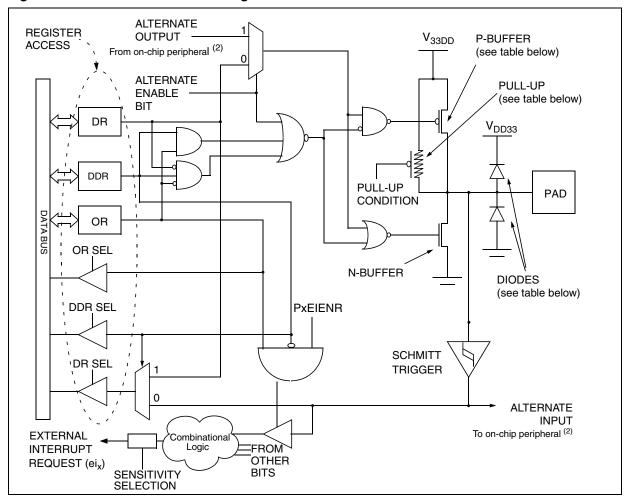

### **6.2 FUNCTIONAL DESCRIPTION**

A Data Register (DR) and a Data Direction Register (DDR) are always associated with each port. The Option Register (OR), which allows input/output options, may or may not be implemented. The following description takes into account the OR register. Refer to the Port Configuration table for Device specific information.

An I/O pin is programmed using the corresponding bits in the DDR, DR and OR registers: bit x corresponding to pin x of the port.

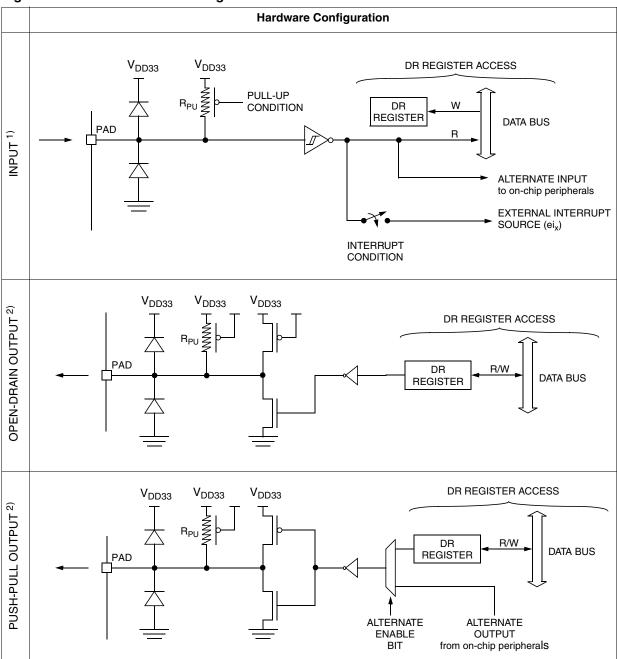

Figure 12 shows the generic I/O block diagram.

### 6.2.1 Input Modes

Clearing the DDRx bit selects input mode. In this mode, reading its DR bit returns the digital value from that I/O pin.

If an OR bit is available, different input modes can be configured by software: floating or pull-up. Refer to I/O Port Implementation section for configuration.

**Note**: Writing to the DR modifies the latch value but does not change the state of the input pin.

### **External Interrupt Function**

In input mode, external interrupts can be enabled by setting the corresponding bit in the PxEIENR register.

Falling or rising edge sensitivity is programmed independently for each interrupt vector. The External Interrupt Control Register (EICR) controls this sensitivity.

Several pins may be tied to one external interrupt vector. Refer to Pin Description to see which ports have external interrupts.

External interrupts are hardware interrupts. Fetching the corresponding interrupt vector automatically clears the request latch. Modifying the sensitivity bits will clear any pending interrupts.

### 6.2.2 Output Modes

Setting the DDRx bit selects output mode. Writing to the DR bits applies a digital value to the I/O through the latch. Reading the DR bits returns the previously stored value.

If an OR bit is available, different output modes can be selected by software: push-pull or opendrain. Refer to I/O Port Implementation section for configuration.

| Table 10. DR value an | d output pin status |

|-----------------------|---------------------|

|-----------------------|---------------------|

| DR | Push-Pull       | Open-Drain      |

|----|-----------------|-----------------|

| 0  | V <sub>OL</sub> | V <sub>OL</sub> |

| 1  | V <sub>OH</sub> | Floating        |

**Note**: When switching from input to output mode, first set the DR bit to set the correct level to be applied on the pin, then write the DDR to configure the pin as an output.

### 6.2.3 Alternate Functions

Many I/Os of the Device have one or more alternate functions to output. This may include output signals from, or input signals to, on-chip peripherals. The Device Pin Description table describes which peripheral signals can be input/output to which ports.

A signal coming from an on-chip peripheral can be output on an I/O. To do this, enable the on-chip peripheral as an output (enable bit in the peripheral's control register). The peripheral configures the I/O as an output and takes priority over standard I/ O programming. The I/O's state is readable by addressing the corresponding I/O data register.

Configuring an I/O as floating enables alternate function input. It is not recommended to configure an I/O as pull-up as this will increase current consumption. Before using an I/O as an alternate input, configure it without interrupt. Otherwise spurious interrupts can occur.

Configure an I/O as input floating for an on-chip peripheral signal which can be input and output.

### Caution:

I/Os which can be configured as both an analog and digital alternate function need special attention. The user must control the peripherals so that the signals do not arrive at the same time on the same pin. If an external clock is used, only the clock alternate function should be employed on that I/O pin and not the other alternate function.

57

# Figure 12. I/O Port General Block Diagram (1)

### Notes:

1. Refer to the Port Configuration table for Device specific information.

2. MSCI can control Port A, B, C and D. See the MSCI I/0 Ports chapter.

# Table 11. ST7 I/O Port Mode Options

| Configuration Mode |                                 |         |          | Diodes                                                   |                    |  |

|--------------------|---------------------------------|---------|----------|----------------------------------------------------------|--------------------|--|

|                    |                                 | Pull-Up | P-Buffer | to V <sub>33 OR</sub> V <sub>DD</sub><br>V <sub>DD</sub> | to V <sub>SS</sub> |  |

| Input              | Floating with/without Interrupt | Off     | Off      |                                                          |                    |  |

| input              | Pull-up with/without Interrupt  | On      |          | 07                                                       |                    |  |

|                    | Push-pull                       | Off     | On       | – On                                                     | On                 |  |

| Output             | Open Drain (logic level)        |         | Off      | 1                                                        |                    |  |

|                    | True Open Drain                 | NI      | NI       | NI (see note)                                            |                    |  |

Legend: NI - not implemented

Off - implemented not activated On - mplemented and activated **Note:** The diode to  $V_{33 \text{ OR}} V_{DD} V_{DD}$  is not implemented in the true open drain pads. A local protection between the pad and  $V_{OL}$  is implemented to protect the device against possible stress.

### Figure 13. Standard I/O Port Configurations

### Notes:

- 1. When the I/O port is in input configuration and the associated alternate function is enabled as an output, reading the DR register will read the alternate function output status.

- 2. When the I/O port is in output configuration and the associated alternate function is enabled as an input, the alternate function reads the pin status given by the DR register content.

### 6.3 ST7 I/O PORT IMPLEMENTATION

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific I/O port features such as ADC input or open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects.

### 6.4 UNUSED I/O PINS

Unused I/O pins must be connected to fixed voltage levels. Refer to the Electrical Characteristics Section.

### 6.5 LOW POWER MODES

| Mode | Description                                                                          |

|------|--------------------------------------------------------------------------------------|

| WAIT | No effect on I/O ports. External interrupts cause the Device to exit from WAIT mode. |

| HALT | No effect on I/O ports. External interrupts cause the Device to exit from HALT mode. |

### **6.6 INTERRUPTS**

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and PxEIENR registers and if the I bit in the CC register is cleared (RIM instruction).

| Interrupt Event                                       | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|-------------------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| External inter-<br>rupt on selected<br>external event | -             | DDRx<br>PxEIENR          | Yes                  | Yes                  |

| Port <sup>1)</sup> | Pin name | Input    |         | Out        | out       |  |

|--------------------|----------|----------|---------|------------|-----------|--|

| FOIL               | OR = 0   |          | OR = 1  | OR = 0     | OR = 1    |  |

| Port A             | PA7:0    | floating | pull-up | open drain | push-pull |  |

| Port B             | PB7:0    | floating | pull-up | open drain | push-pull |  |

| Port C             | PC7:0    | floating | pull-up | open drain | push-pull |  |

| Port D             | PD7:0    | floating | pull-up | open drain | push-pull |  |

| Port E             | PE7:0    | floating | pull-up | open drain | push-pull |  |

### Table 12. ST7 I/O Port Configuration

### Note:

1) Ports unavailable in the 48-pin packages (PB7:0, PD7:5, PE6:4) are forced to input mode with internal pull-up activated to avoid possible floating I/O consumption.

### **6.7 REGISTER DESCRIPTION**

### DATA REGISTER (DR)

Port x Data Register PxDR with x = A, B, C, D or E.

### Read/Write

Reset Value: 0000 0000 (00h)

| 7 |  |  |  |

|---|--|--|--|

|   |  |  |  |

0

0

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |

Bits 7:0 = **D**[7:0] *Data register 8 bits.*

The DR register has a specific behaviour according to the selected input/output configuration. Writing the DR register is always taken into account even if the pin is configured as an input; this allows to always have the expected level on the pin when toggling to output mode. Reading the DR register always returns the digital value applied to the I/O pin (pin configured as input).

### Note:

For this register, bits corresponding to I/O ports which are unavailable in the 48-pin package are read as 1.

### DATA DIRECTION REGISTER (DDR)

Port x Data Direction Register PxDDR with x = A, B, C, D or E. Read/Write

Reset Value: 0000 0000 (00h)

7

57/

| DD7 | פחח |     | עםם | 200 | כחח |     | ססס |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 007 | 000 | 005 | 004 | 005 | 002 | 001 | 000 |

|     |     |     |     |     |     |     |     |

Bits 7:0 = **DD[7:0]** Data direction register 8 bits.

The DDR register gives the input/output direction configuration of the pins. Each bit is set and cleared by software.

0: Input mode 1: Output mode

### **OPTION REGISTER (OR)**

Port x Option Register

PxOR with x = A,B, C, D, or E.

Read/Write

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |  |

|----|----|----|----|----|----|----|----|--|

| 07 | O6 | O5 | 04 | O3 | 02 | 01 | 00 |  |

Bits 7:0 = **O**[7:0] Option register 8 bits.

For specific I/O pins, this register is not implemented. In this case the DDR register is enough to select the I/O pin configuration.

The OR register allows to distinguish: in input mode if the interrupt capability or the basic configuration is selected, in output mode if the push-pull or open drain configuration is selected.

Each bit is set and cleared by software. Input mode:

0: Floating input

1: Floating input with interrupt.

Output mode:

0: Output open drain (with P-Buffer deactivated)

1: Output push-pull

| Address<br>(Hex.) | Register<br>Label <sup>1) 2)</sup> | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|------------------------------------|-----|---|---|---|---|---|---|-----|

|                   | t Value<br>ort registers           | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0026h             | PADR                               | MSB |   |   |   |   |   |   | LSB |

| 0027h             | PADDR                              |     |   |   |   |   |   |   |     |

| 0028h             | PAOR                               |     |   |   |   |   |   |   |     |

| 0029h             | PBDR                               | MSB |   |   |   |   |   |   | LSB |

| 002Ah             | PBDDR                              |     |   |   |   |   |   |   |     |

| 002Bh             | PBOR                               |     |   |   |   |   |   |   |     |

| 002Ch             | PCDR                               | MSB |   |   |   |   |   |   | LSB |

| 002Dh             | PCDDR                              |     |   |   |   |   |   |   |     |

| 002Eh             | PCOR                               |     |   |   |   |   |   |   |     |

| 002Fh             | PDDR                               | MSB |   |   |   |   |   |   | LSB |

| 0030h             | PDDDR                              |     |   |   |   |   |   |   |     |

| 0031h             | PDOR                               |     |   |   |   |   |   |   |     |

| 0032h             | PEDR                               | MSB |   |   |   |   |   |   | LSB |

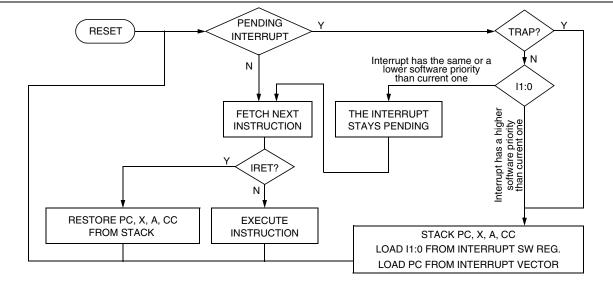

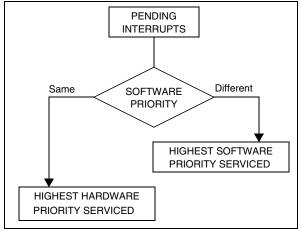

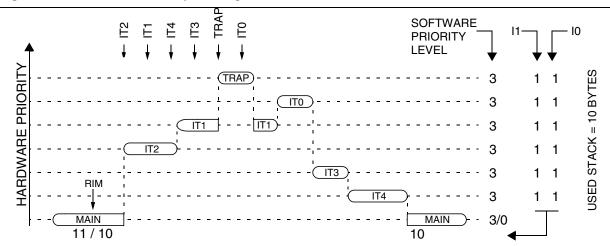

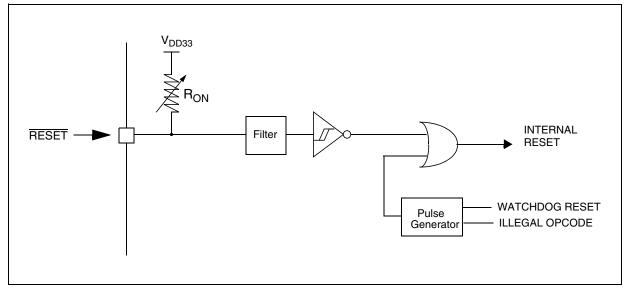

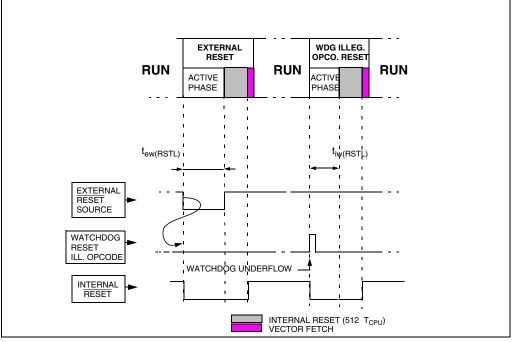

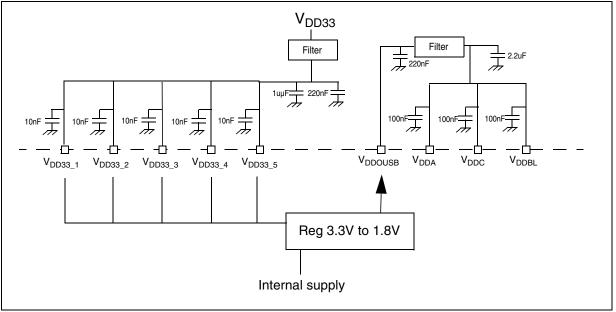

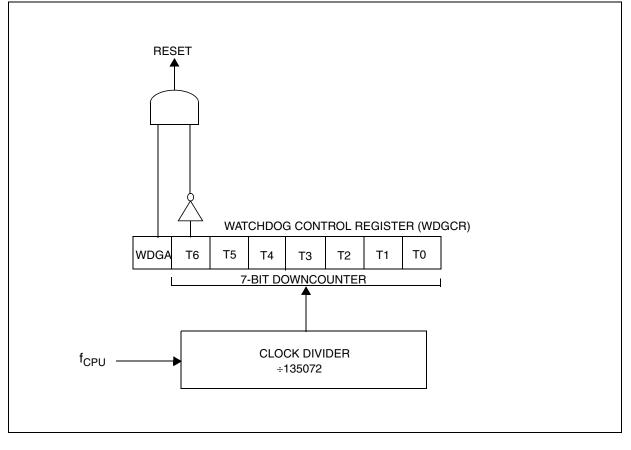

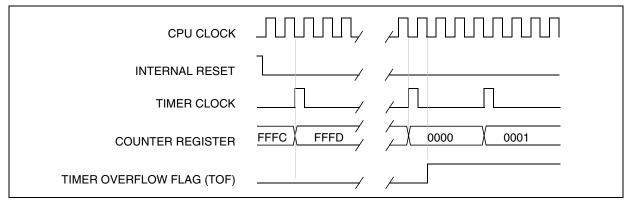

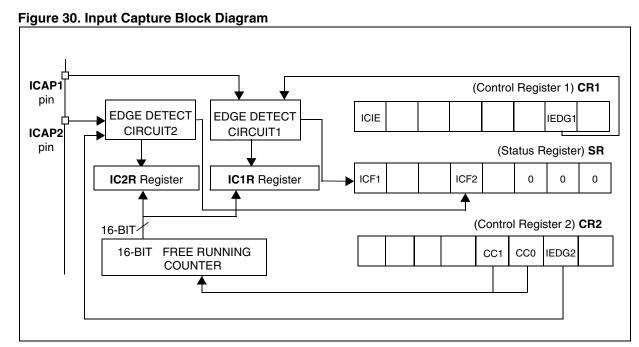

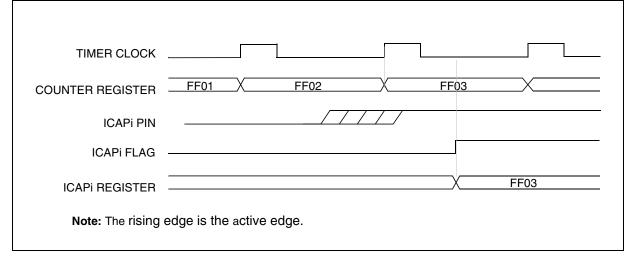

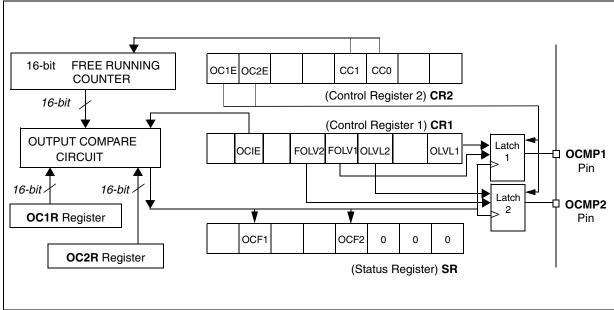

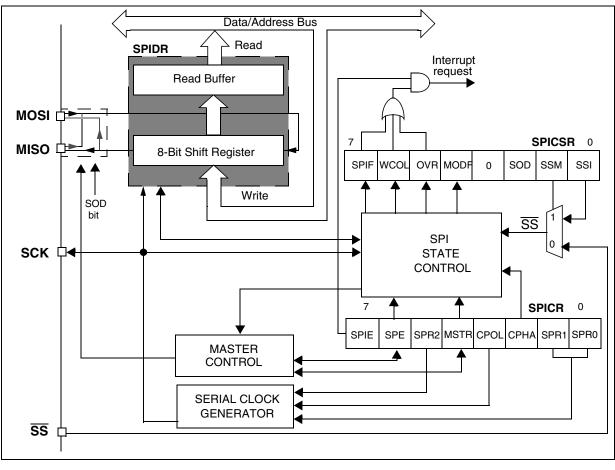

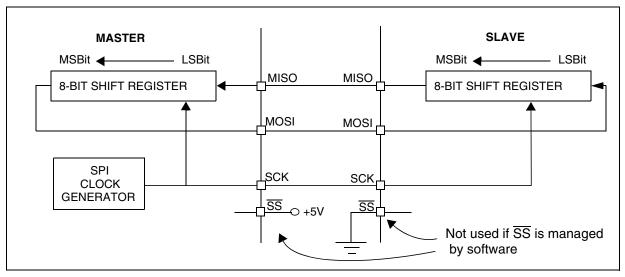

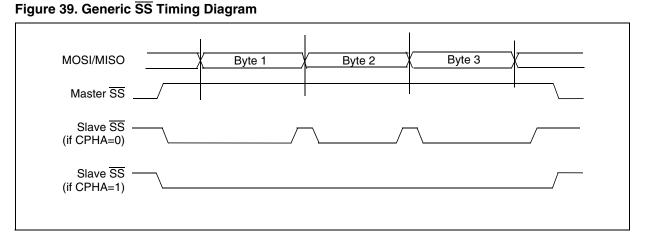

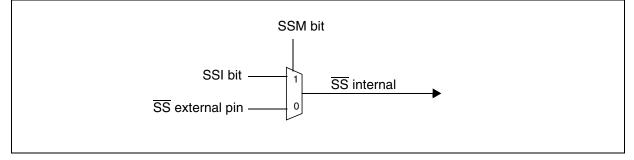

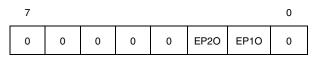

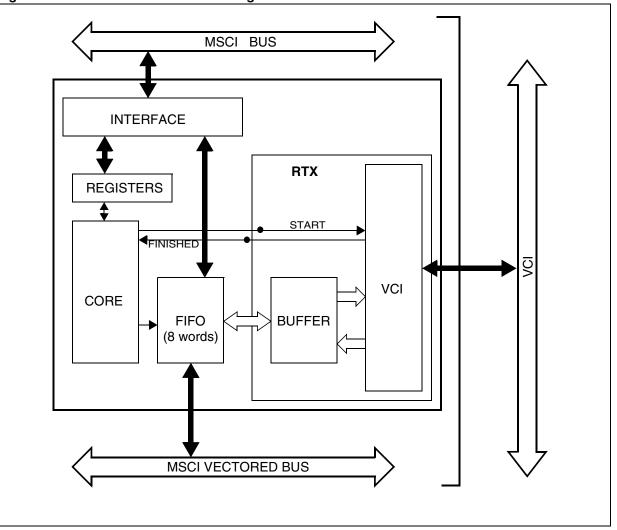

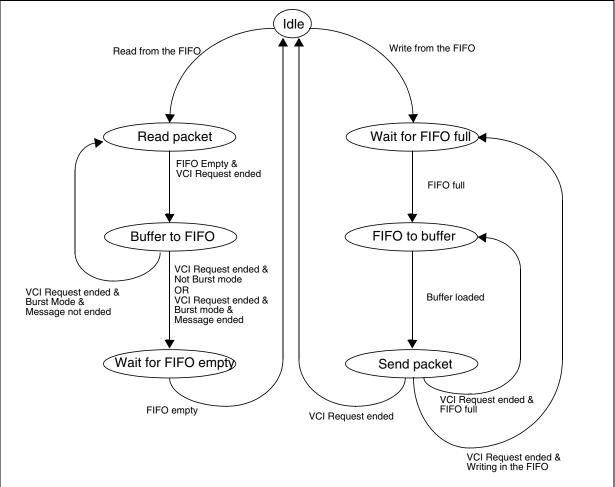

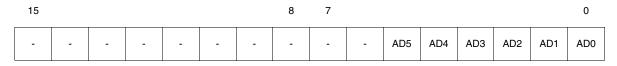

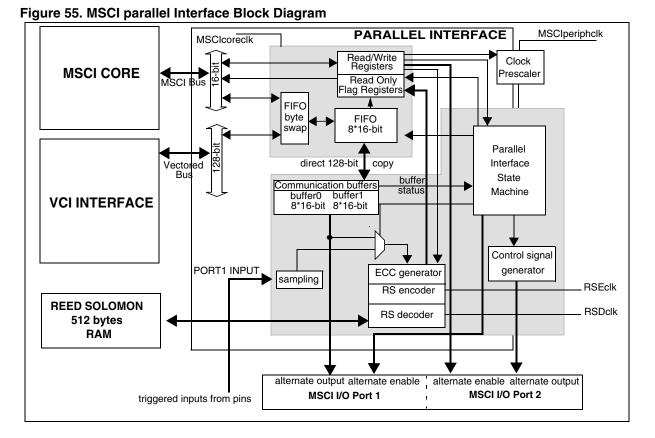

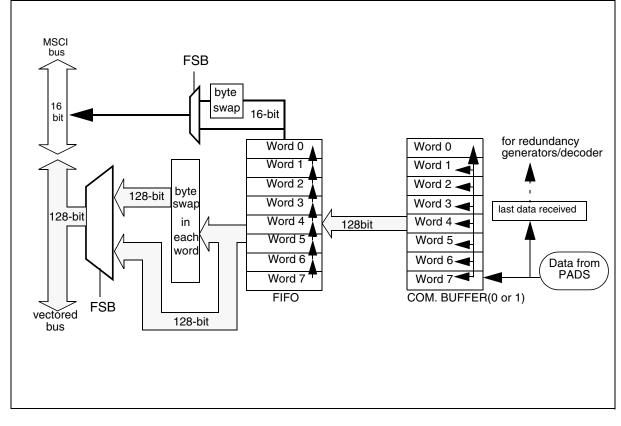

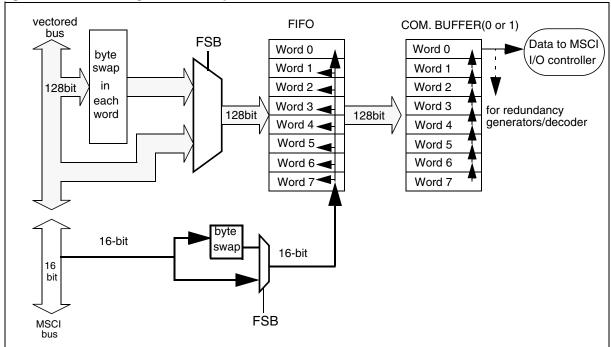

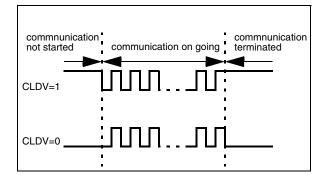

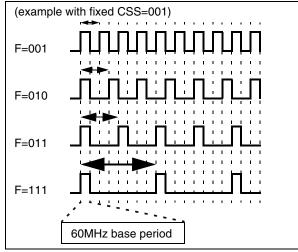

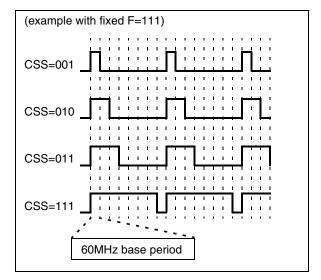

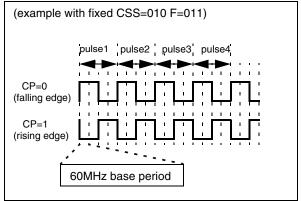

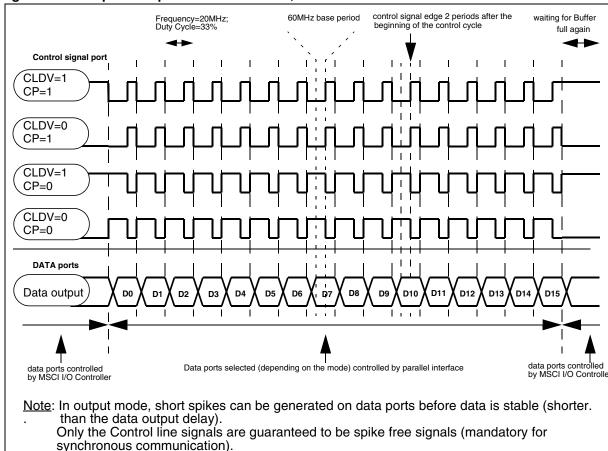

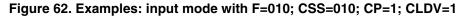

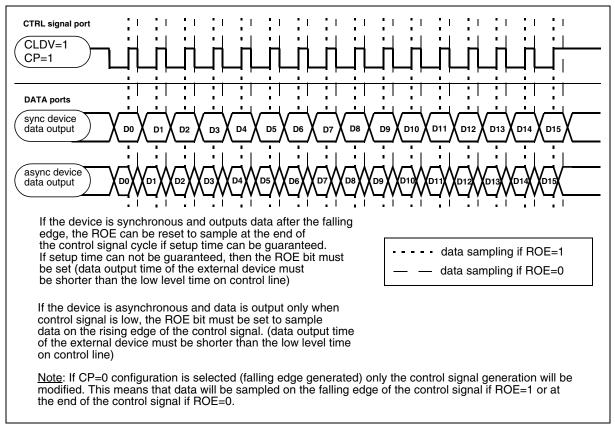

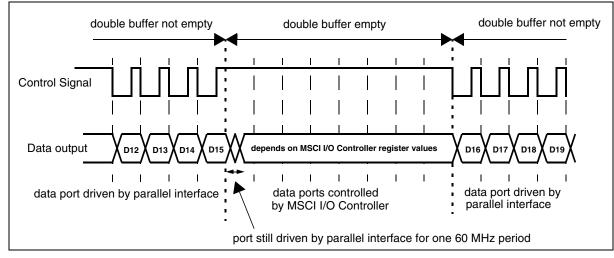

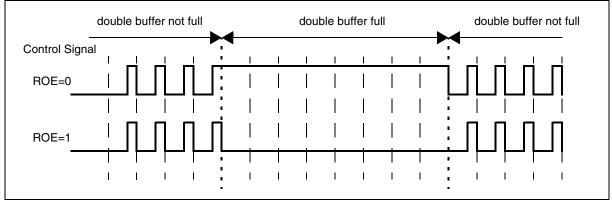

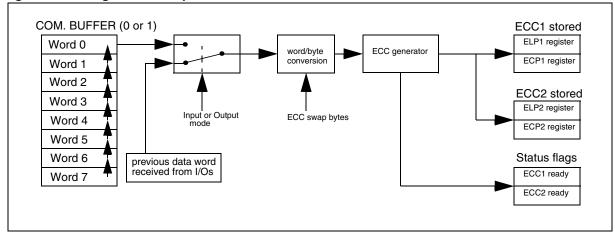

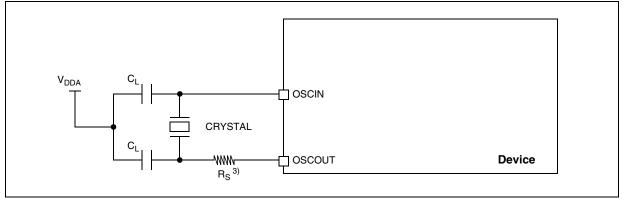

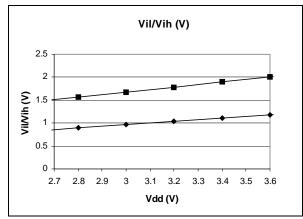

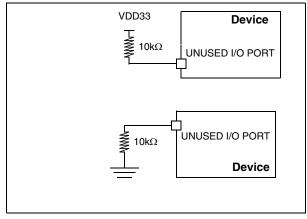

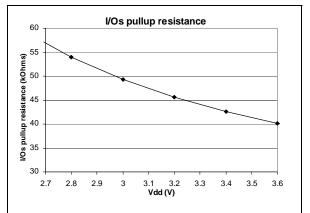

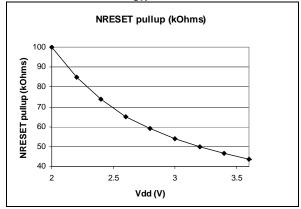

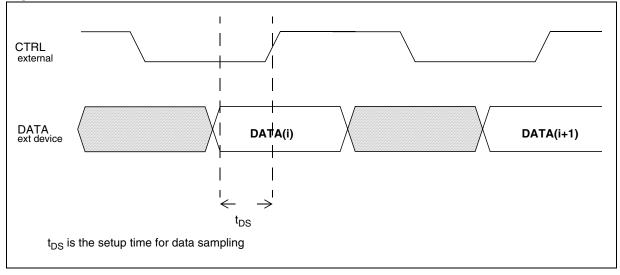

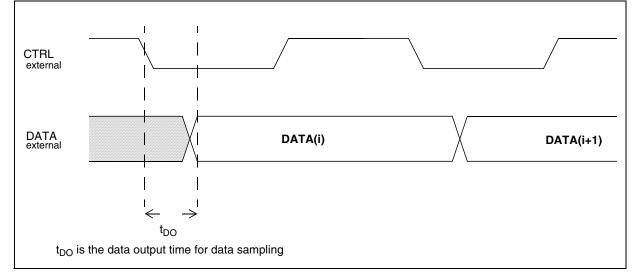

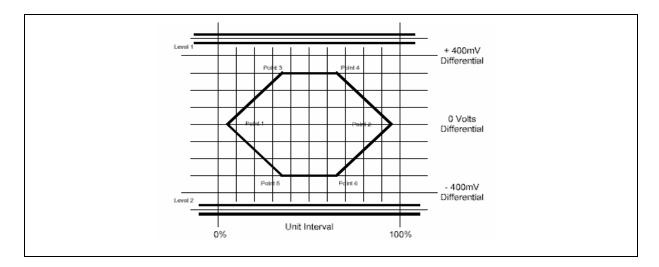

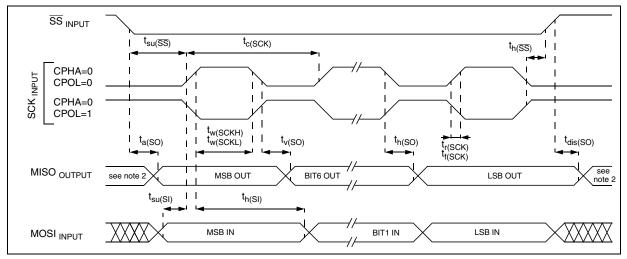

| 0033h             | PEDDR                              |     |   |   |   |   |   |   |     |